Silverr12/DMA-CFW-Guide

GitHub: Silverr12/DMA-CFW-Guide

Stars: 1002 | Forks: 177

# DMA-CFW 指南

本指南详细介绍了基于 [pcileech-fpga](https://github.com/ufrisk/pcileech-fpga) **版本 4.15** 制作修改版 DMA(攻击)固件的说明。

#### 📖为什么要制作本指南? 我不喜欢有些人故意含糊其辞,对信息保密,甚至误导他人,使他们无法自己制作固件,最终只能花费数百美元从其他提供商那里购买无法保证质量的自定义固件。 #### 设备兼容性 本指南使用 squirrel DMA 卡。项目请勿使用 Squirrel 文件夹,而是使用你的 DMA 卡对应的文件夹,该文件夹位于 pcileech-fpga-master 文件夹中。 - 35T: Squirrel - 75T: EnigmaX1 - 100T: ZDMA #### 🔎 定义 __DMA__ : Direct Memory Access(直接内存访问) __TLP__ : Transaction Layer Packet(事务层报文) __DSN__ : Device Serial Number(设备序列号) __DW__ : Double Word | DWORD(双字) __Donor card__ : 供应卡(Donor card),用于获取 ID/配置空间,不会在你的主 PC 上使用(例如 PCIE Wifi 卡) __FPGA__ : Field Programmable Gate Array(现场可编程门阵列) ### ⚠️ 免责声明 - 本指南并不总是更新到圈内的最佳实践,实测时请务必谨慎。

- 本指南___不___详述如何设置软件或更改计算机设置以适配 DMA 卡 - 如果你在阅读完整个指南后仍有不理解的概念,底部有一个 Discord 服务器链接 ### 📑 目录 1. [要求](https://github.com/Silverr12/DMA-FW-Guide#1-requirements) 2. [收集供应卡信息](https://github.com/Silverr12/DMA-FW-Guide#2-gathering-the-donor-information) 3. [初始自定义](https://github.com/Silverr12/DMA-FW-Guide#3-initial-customisation) 4. [Vivado 项目自定义](https://github.com/Silverr12/DMA-FW-Guide#4-vivado-project-customisation) 5. [其他配置空间更改](https://github.com/Silverr12/DMA-CFW-Guide#5-other-config-space-changes) 6. [TLP 模拟](https://github.com/Silverr12/DMA-CFW-Guide#6-tlp-emulation) 7. [中断](https://github.com/Silverr12/DMA-CFW-Guide#7-interrupts) 8. [构建、刷写与测试](https://github.com/Silverr12/DMA-CFW-Guide#7-building-flashing--testing) ## **1. 要求** #### 硬件 - 一张供应卡(下文解释) - 当然还有一张 DMA 卡 #### 软件 - 文本编辑器,本指南使用 [Visual Studio](https://visualstudio.microsoft.com/vs/community/)。 - [Xilinx Vivado](https://www.xilinx.com/support/download.html) 需要注册 AMD 账号才能下载 - [Pcileech-fpga](https://github.com/ufrisk/pcileech-fpga) 自定义固件源码 - [Arbor](https://www.mindshare.com/software/Arbor) 需要注册账号才能下载试用版(14 天)

可以通过删除注册表编辑器中的相应文件夹来延长试用期,但我不能告诉你更多了。 - Arbor 的替代品,[Telescan PE](https://www.teledynelecroy.com/protocolanalyzer/pci-express/telescan-pe-software/resources/analysis-software),这个非常相似且完全免费,但注册需要人工审核,可能需要一点时间。 ## **2. 收集供应卡信息** (使用供应卡将有助于我们稍后进行 TLP 模拟,与设备通信以启动驱动程序从而增加合法性)

由于我的测试和知识有限,接下来的所有示例我将使用网络适配器

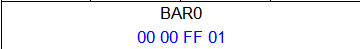

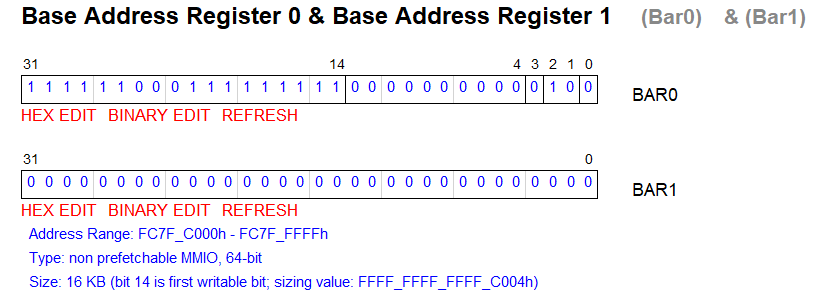

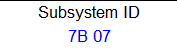

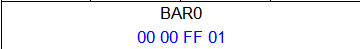

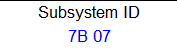

(如果你知道自己在做什么并了解其中的细微差别,完全可以跳过购买供应卡这一步,但对于新手我强烈建议这样做,花 20 美元换来一个保证能用的产品,比针对延迟检测波进行特定测试要好得多) 建议使用廉价的硬件来获取 ID,然后将其丢弃。这些用于模拟 DMA 卡。**所以不要获取你电脑中任何现有硬件的 ID 并将其插入固件中。因为很可能在未来,如果现在还没有的话,拥有 2 个 1:1 ID 的设备会被检测并标记** ### 使用 Arbor 转到 Local system(本地系统)选项卡下的 Scan Options(扫描选项),按 Scan/Rescan(扫描/重新扫描),默认选中的值对我们来说已经足够了。 进入 PCI Config(PCI 配置)找到你的网络控制器,在 decode(解码)部分滚动查看,并记录以下内容: #### 下面显示的所有 ID 都是我的,你的可能不一样 1. Device ID(设备 ID)  2. Vendor ID(厂商 ID)  3. Revision ID(版本 ID,显示为 RevID)  4. BAR0 Sizing Value(大小值)(1/2/3/4/5 如果你有的话)  点击它所在的方框查看大小信息  我的大小是 16kb,记录下来 5. Subsystem ID(子系统 ID)  6. DSN(列为 Serial Number Register)  合并你的低位和高位 DSN 寄存器,用于我们在第 3 步中的 DSN 配置 例如,这些是我的值: Serial Number Register (Upper DW): `01 00 00 00`

Serial Number Register (Lower DW): `68 4C E0 00`

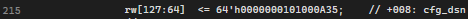

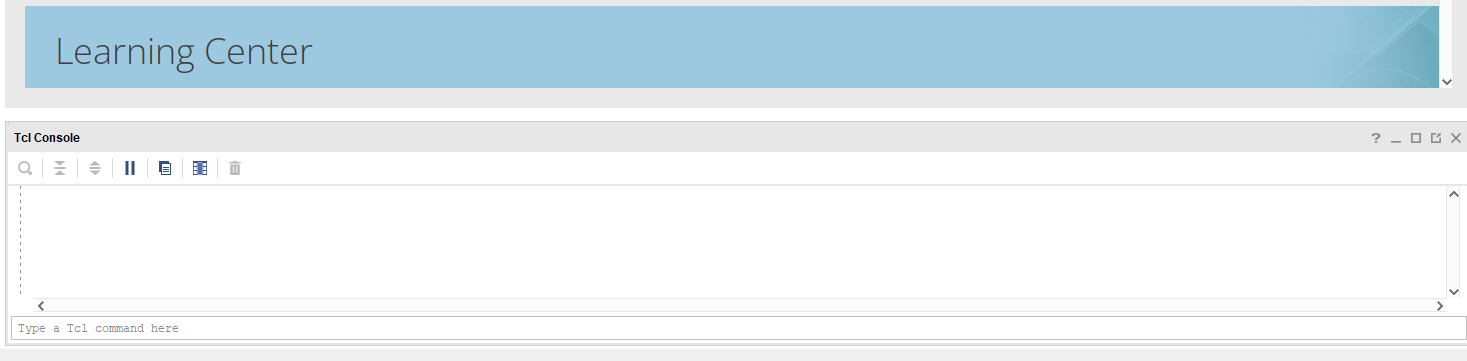

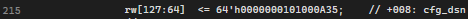

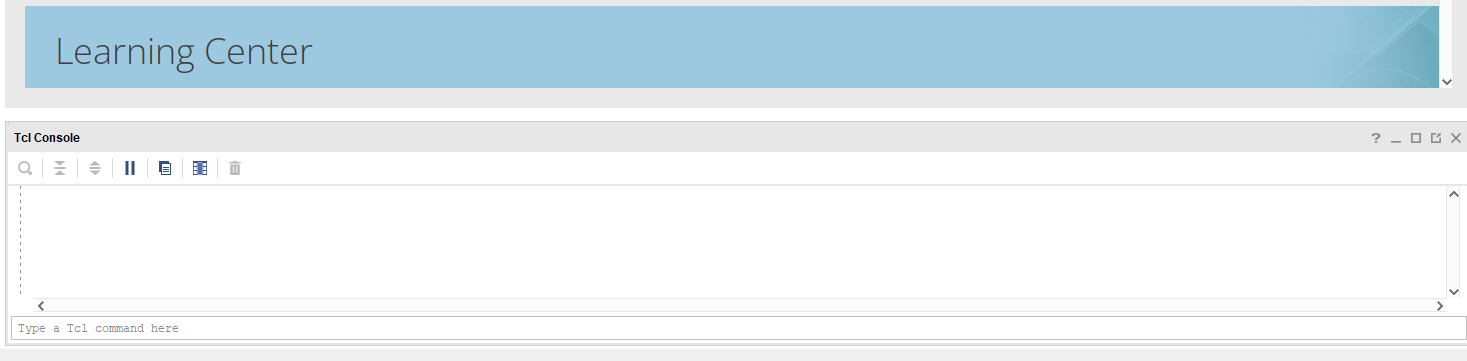

以相同的格式合并你的值: Upper DW + Lower DW = `01 00 00 00 68 4C E0 00` ## **3. 初始自定义** 再次由于知识有限,目前我将专注于 pcileech 的 PCIeSquirrel 部分,对于使用其他固件的人表示歉意。 ### 使用 Visual Studio 1. 打开 PCIeSquirrel 文件夹并转到文件 `/PCIeSquirrel/src/pcileech_pcie_cfg_a7.sv`。在此文件中使用 Ctrl+F 搜索 `rw[20]`,该值应该在第 209 行,以找到主中止标志/自动清除状态寄存器。将随后的 0 改为 1。 之前  之后  2. 在同一个文件 `pcileech_pcie_cfg_a7.sv` 中,Ctrl+F 搜索 `rw[127:64]`,应该在第 215 行,找到列为 `rw[127:64] <= 64'h0000000101000A35; // cfg_dsn` 的 DSN 字段,在那里插入你的 Serial Number,格式如 `rw[127:64] <= 64'hXXXXXXXXXXXXXXXX; // cfg_dsn`,保持输入字段 16 个字符的长度,如果你的 DSN 较短,请插入零,如示例图像所示。 之前  之后  这是我的 DSN 如果你的供应卡没有 DSN,你的应该是这样 `rw[127:64] <= 64'h0000000000000000; // +008: cfg_dsn` 4. 继续保存你所做的所有更改 ### 生成 Vivado 文件 1. 打开 Vivado,在顶部菜单的搜索查询中,搜索 tcl console 并点击它。  控制台现在应该在应用程序底部打开。  2. 在 Tcl 控制台中,输入 `pwd` 查看工作目录。它应该看起来像这样 `C:/Users/user/AppData/Roaming/Xilinx/Vivado` 3. cd 到 pcileech-fpga-master 项目文件夹中的 PCIeSquirrel 文件夹。它应该看起来像这样 `C:\Users\user\Desktop\pcileech-fpga-master\PCIeSquirrel`。(桌面是我的项目文件夹所在的位置)

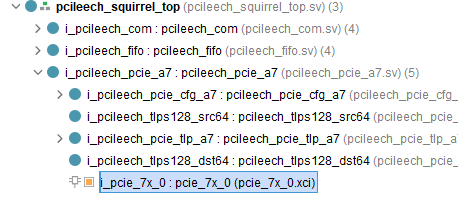

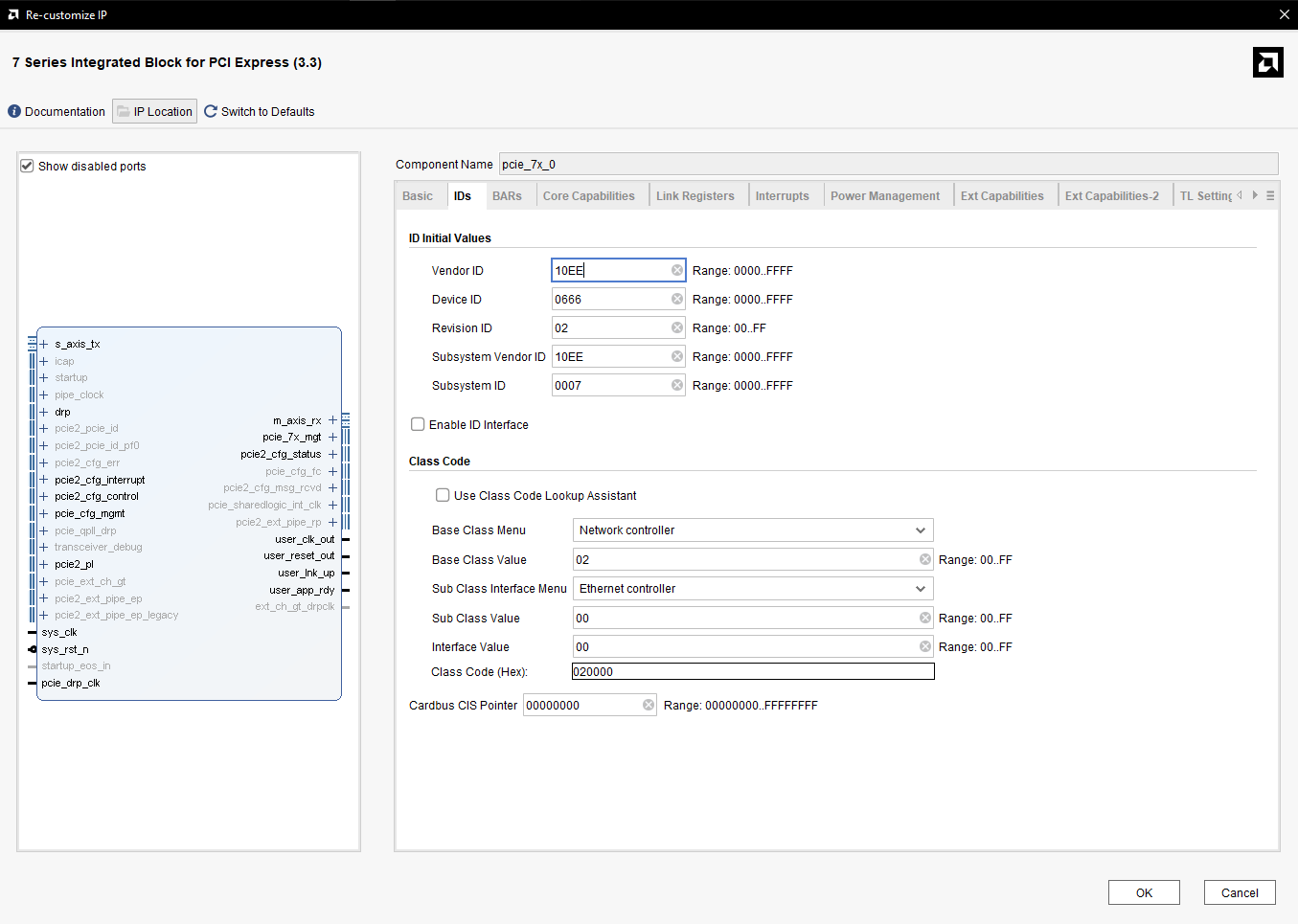

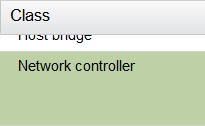

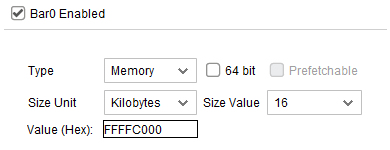

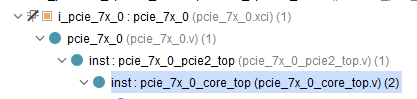

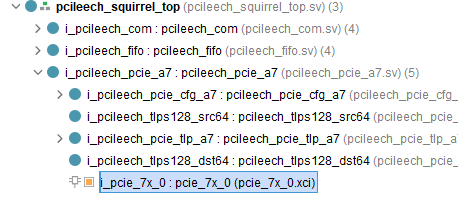

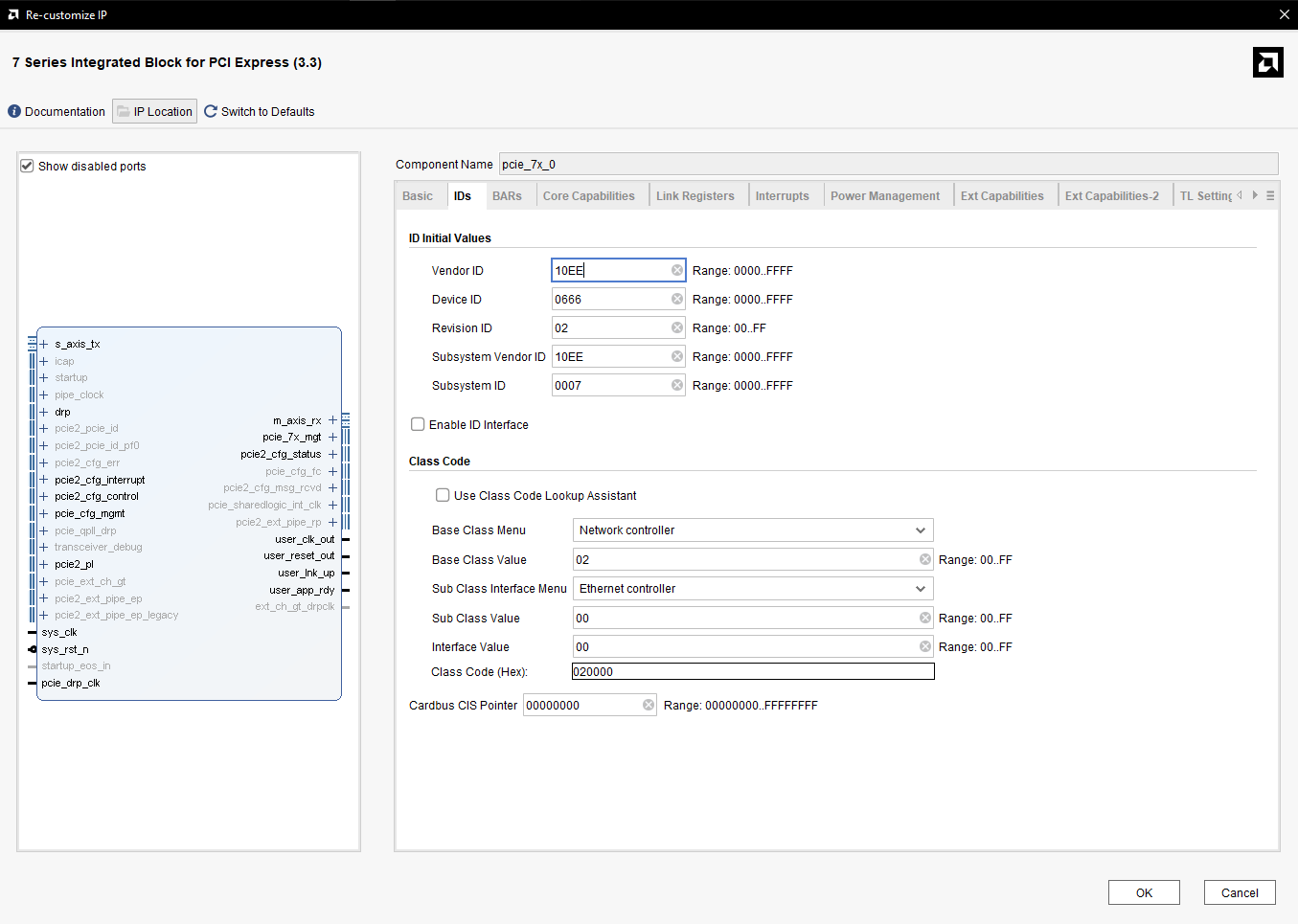

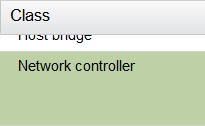

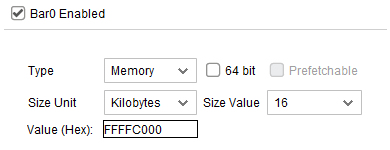

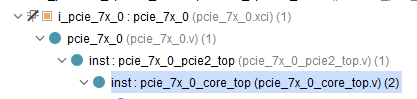

如果尝试 cd 到项目目录时出现错误,请将所有 '\\' 替换为 '/' 4. 打开 PCIeSquirrel 目录后,在 Tcl 控制台中输入 `source vivado_generate_project.tcl -notrace` 并等待它完成 5. 项目生成后,Vivado 应自动打开 `pcileech_squirrel.xpr` 文件。先将其保持打开状态。 ## **4. Vivado 项目自定义** 1. 进入 Vivado 后,导航到 "sources" 框并按如下顺序导航 `pcileech_squirrel_top` > `i_pcileech_pcie_a7 : pcileech_pcie_a7` 然后双击带有黄色方块的文件,标记为 `i_pcie_7x_0 : pcie_7x_0`。  2. 你现在应该在一个名为 "Re-customize IP" 的窗口中,在那里,按下 `IDs` 选项卡并输入你从供应板收集的所有 ID,还要注意 "SubSystem Vendor ID" 与你的 Vendor ID 相同。_(如果你的供应板与网络适配器不同,你可能还需要调整下面 "Class Code" 部分的一些设置。)_  要检查供应卡的 class code,请回到 Arbor > 如有需要则扫描,否则 > PCI config > 将 PCI view 设置为 Linear。你的卡应该以绿色高亮显示。还会有一列名为 **Class** 的标题。将其与你的卡匹配。  3. 同时进入 "BARs" 选项卡并设置你在第 2 步收集的大小值,注意显示的 Hex Value 并不意味着要与你的 bar 地址相同。你无法编辑此值。  我的 bar 大小是 16kb,所以你将其设置为 16kb 如果大小单位不同,请更改大小单位以适应 bar 大小的单位 4. 在右下角按 OK,然后在弹出的新窗口中点击 "Generate" 并等待其完成。

5. 我们将锁定核心,以便当 Vivado 综合 and/or 构建我们的项目时,它不会覆盖某些内容,并允许我们手动编辑一些以前只能通过界面完成的事情,为此,导航到底部框右上 "Tcl Console" 并在其中输入 `set_property is_managed false [get_files pcie_7x_0.xci]`,(为了任何目的在未来解锁它,请使用 `set_property is_managed true [get_files pcie_7x_0.xci]`)。 # **第 5 步和第 6 步** 目前正在研究和修订中,因此尚未完成或定稿。请谨慎行事。 ## **5. 其他配置空间更改** 1. 在 Vivado 中,如图所示导航到 `pcie_7x_0_core_top`,并使用文本编辑器左上角的放大镜搜索这些不同的行,以使它们与你的供应卡匹配  #### - 以下是在手动 Vivado IP 核配置中的变量名称列表,它们对应于我们已经确认**不会**破坏固件的值,你可以更改这些值以匹配你的供应卡,我们能够通过 Arbor 的名称进行匹配。按能力匹配,包括:

- (PM) `PM_CAP_VERSION`, `PM_CAP_D1SUPPORT`,`PM_CAP_AUXCURRENT`, `PM_CSR_NOSOFTRST` - (MSI) `MSI_CAP_64_BIT_ADDR_CAPABLE`, - (PCIe) `PCIE_CAP_DEVICE_PORT_TYPE`, `DEV_CAP_MAX_PAYLOAD_SUPPORTED`, `DEV_CAP_EXT_TAG_SUPPORTED`, `DEV_CAP_ENDPOINT_L0S_LATENCY`, `DEV_CAP_ENDPOINT_L1_LATENCY`, `LINK_CAP_ASPM_SUPPORT`, `LINK_CAP_MAX_LINK_SPEED`, `LINK_CAP_MAX_LINK_WIDTH`, `LINK_CTRL2_TARGET_LINK_SPEED` - 可以在不同文件或我还不知道的 GUI 中更改的字段。

- (PM) `cfg_pmcsr_powerstate` - (PCIe) `corr_err_reporting_en`, `non_fatal_err_reporting_en`, `fatal_err_reporting_en`, `no_snoop_en`, `Link Status2: Current De-emphasis` #### - 还建议更改某些功能的块位置,这可以通过更改以下变量来完成: - Capability NEXT Pointers:`CAPABILITIES_PTR`, `MSI_CAP_NEXTPTR`, `PCIE_CAP_NEXTPTR`, `PM_CAP_NEXTPTR` 和 - Capability Pointers: `MSI_BASE_PTR`, `PCIE_BASE_PTR`, `PM_BASE_PTR` 在默认的 pcileech 固件中,你可以找到:**PM 在 0x40,MSI 在 0x50,PCIe 在 0x60**,示例将把它们更改为 **PCIe 在 0x40,PM 在 0xC8 和 MSI 在 0xD0**,但实际上你可以将它们放在任何位置(例如 PCIe 在 0x80,PM 在 0xD0 和 MSI 在 0x90),因为我们的计算机可以并且会跳过空块,你所要做的就是确保 `NEXTPTR` 连接到下一个功能,如下所述,并注意功能大小,以免它们试图重叠。 - 你需要你的 NEXTPTR 从 0x00 的头部开始按顺序排列,并在配置块中向上增加,例如: - 如果我要将我的功能块更改为 `PCIe: 0x40 | PM: 0xC8 | MSI: 0xD0`,我只需将其关联的 `BASE_PTR` 变量分配为相同的值。始终确保从 0x40 或以上开始,因为我们的头部刚好在它之前结束,并且还要确保你的 base ptrs 总是以 0、4 或 8 结尾,例如 40、44 68。 - 其次,我还必须让我的头部 capability pointer `CAPABILITIES_PTR` 指向 40(默认情况下就是这样),因为在这种情况下它是我们要读取的最低/第一个,然后 `PCIE_CAP_NEXTPTR` 将指向 C8,`PM_CAP_NEXTPTR` 指向 D0,`MSI_CAP_NEXTPTR` 指向 00 以结束它,并且始终确保它是从上到下的顺序,如果你尝试在配置空间中向后指向,你的固件在某些情况下将无法工作。(扩展功能如 AER、DSN、LTR 等如果你决定放入它们也需要此配置。但你不要将常规功能指向它们,因为它们是一个单独的‘集合’,除此之外它们遵循与常规功能相同的指针格式。) ## **6. TLP 模拟** 目前你只更改了静态设备属性。然而,正如你在 Windows 设备管理器中看到的黄色警告标志所示,它们并没有与实际设备驱动程序通信。要模拟实际设备,你必须模拟由原始设备的 BAR 定义的内存区域中存储的值。 你可以使用这个小型 C 程序以有用的 verilog 格式复制内存值和相应的地址: ``` #include

#include

#include

#include

#include

#include

#include

#include

#include

#include

#include

#include

uint8_t main(int argc, char **argv)

{

uint32_t sys_handle = open(argv[1], O_RDWR | O_SYNC);

printf("Opening File : %s\n", argv[1]);

uint8_t type_width = sizeof(uint32_t);

if (sys_handle == -1)

{

printf("Failed to open with error : %s\n", strerror(errno));

return EXIT_FAILURE;

}

off_t target = 0;

off_t target_base = target & ~(sysconf(_SC_PAGE_SIZE) - 1);

uint32_t map_size = 4096UL;

void *map_base = mmap(0, map_size, PROT_READ | PROT_WRITE, MAP_SHARED, sys_handle, target_base);

printf("PCI Memory mapped to: 0x%08lx.\n", (unsigned long) map_base);

for (uint16_t i = 0; i < 0x1000 / type_width + 1; i += 1)

{

uint32_t read_result = *((uint32_t *)(map_base + i * type_width + target - target_base));

printf("16'h%04X : rd_rsp_data <= 32'h%08X;\n", (uint32_t)(i * type_width + target), read_result);

}

return EXIT_SUCCESS;

}

```

只需使用 `gcc bar.c -o bar` 编译程序,并使用 `./bar /sys/bus/pci/devices/0000:xx:xx.x/resource0` 运行它。将 `0000:xx:xx.x` 替换为你的原始 PCIe 设备的路径。

输出应该如下所示:

```

$ sudo ./bar /sys/bus/pci/devices/0000:03:00.0/resource0

Opening File : /sys/bus/pci/devices/0000:03:00.0/resource0

PCI Memory mapped to: 0x7f86b120c000.

16'h0000 : rd_rsp_data <= 32'h01110010;

16'h0004 : rd_rsp_data <= 32'h00000000;

16'h0008 : rd_rsp_data <= 32'h00A1088F;

16'h000C : rd_rsp_data <= 32'h0000003F;

16'h0010 : rd_rsp_data <= 32'h0000003F;

16'h0014 : rd_rsp_data <= 32'h80000000;

16'h0018 : rd_rsp_data <= 32'h04048278;

16'h001C : rd_rsp_data <= 32'h31233434;

16'h0020 : rd_rsp_data <= 32'hF000B222;

16'h0024 : rd_rsp_data <= 32'h00110696;

16'h0028 : rd_rsp_data <= 32'h00000001;

16'h002C : rd_rsp_data <= 32'h00000000;

... more

16'h0FF4 : rd_rsp_data <= 32'hFFFFFFFF;

16'h0FF8 : rd_rsp_data <= 32'hFFFFFFFF;

16'h0FFC : rd_rsp_data <= 32'hFFFFFFFF;

16'h1000 : rd_rsp_data <= 32'h00000000;

```

现在你只需要修改 `pcileech_tlps128_bar_controller.sv` 中的 BAR controller,主要是添加 `input [31:0] base_address_register` 和一个 `case` 语句,修复每个 8 位块在 32 位地址中的 MSB / LSB 顺序,并在调用相应地址时返回内存值。

```

module pcileech_bar_impl_zerowrite4k(

input rst,

input clk,

input [31:0] wr_addr,

input [3:0] wr_be,

input [31:0] wr_data,

input wr_valid,

input [87:0] rd_req_ctx,

input [31:0] rd_req_addr,

input rd_req_valid,

input [31:0] base_address_register,

output bit [87:0] rd_rsp_ctx,

output bit [31:0] rd_rsp_data,

output bit rd_rsp_valid

);

bit [87:0] drd_req_ctx;

bit [31:0] drd_req_addr;

bit drd_req_valid;

bit [31:0] dwr_addr;

bit [31:0] dwr_data;

bit dwr_valid;

bit [31:0] data_32;

time number = 0;

always @ ( posedge clk ) begin

if (rst)

number <= 0;

number <= number + 1;

drd_req_ctx <= rd_req_ctx;

drd_req_valid <= rd_req_valid;

dwr_valid <= wr_valid;

drd_req_addr <= rd_req_addr;

rd_rsp_ctx <= drd_req_ctx;

rd_rsp_valid <= drd_req_valid;

dwr_addr <= wr_addr;

dwr_data <= wr_data;

if (drd_req_valid) begin

case (({drd_req_addr[31:24], drd_req_addr[23:16], drd_req_addr[15:08], drd_req_addr[07:00]} - (base_address_register & ~32'h4)) & 32'hFFFF)

//The code block you received from the C code

16'h0000 : rd_rsp_data <= 32'h01110010;

16'h0004 : rd_rsp_data <= 32'h00000000;

16'h0008 : rd_rsp_data <= 32'h00A1088F;

16'h000C : rd_rsp_data <= 32'h0000003F;

16'h0010 : rd_rsp_data <= 32'h0000003F;

16'h0014 : rd_rsp_data <= 32'h80000000;

16'h0018 : rd_rsp_data <= 32'h04048278;

16'h001C : rd_rsp_data <= 32'h31233434;

16'h0020 : rd_rsp_data <= 32'hF000B222;

16'h0024 : rd_rsp_data <= 32'h00110696;

16'h0028 : rd_rsp_data <= 32'h00000001;

16'h002C : rd_rsp_data <= 32'h00000000;

... more

16'h0FF4 : rd_rsp_data <= 32'hFFFFFFFF;

16'h0FF8 : rd_rsp_data <= 32'hFFFFFFFF;

16'h0FFC : rd_rsp_data <= 32'hFFFFFFFF;

16'h1000 : rd_rsp_data <= 32'h00000000;

default : rd_rsp_data <= 32'h00000000;

endcase

end

end

endmodule

```

**另请参阅:**

1. [Ekknod 的 bar controller 配置](https://github.com/ekknod/pcileech-wifi/blob/main/src/pcileech_tlps128_bar_controller.sv#L850) 第 850-896 行作为示例

2. [Yxlnq 的 bar controller 之一](https://github.com/yxlnqs/diviner-full-emu-v2/blob/5a177e34ae5dae94bb2c023e38301af425ca6e4b/src/pcileech_tlps128_bar_controller.sv#L850)

### 一般理解与 TLP 模拟资源

1. https://fpgaemu.readthedocs.io/en/latest/emulation.html

2. https://docs.xilinx.com/v/u/en-US/pcie_blk_plus_ug341

3. https://www.fpga4fun.com/PCI-Express4.html

4. https://www.xillybus.com/tutorials/pci-express-tlp-pcie-primer-tutorial-guide-1

5. https://ctf.re (<-很棒的一个)

## **7. 中断**

请暂时参阅 [https://github.com/kilmu1337/VGK-DMA-BYPASS](https://github.com/kilmu1337/VGK-DMA-BYPASS)

## **8. 构建、刷写与测试**

1. 在 tcl 控制台中运行 `source vivado_build.tcl -notrace` 以生成你需要刷写到卡上的文件

- 你会在 `pcileech_squirrel/pcileech_squirrel.runs/impl_1` 中找到该文件,名为 "pchileech_squirrel_top.bin"

- 按照 [LambdaConcept 官方刷写指南](https://docs.lambdaconcept.com/screamer/programming.html) 中的步骤操作 **提醒:仅适用于 SQUIRREL** 3. 从你的第二台计算机运行 DMA 速度测试工具 (Discord 服务器中有链接和下载) 以验证你的固件是否正常工作并按预期读取。 4. 转储你新固件的配置空间,并与下面显示的 **已知** 签名的 pcileech 默认值进行比较,看看是否过于相似。你绝对应该正确看待某些值相同这一事实,你必须考虑到除了序列号和可能的 bar 地址之外,一种类型的(例如)网络卡的配置空间在所有这些卡中都是相同的。GLHF 这是低端检测系统据称在 PCIe 设备的配置空间中扫描的签名之一: [更多信息在这里](https://dma.lystic.dev/anticheat-evasion/detection-vectors)

`40: 01 48 03 78 08 00 00 00 05 60 80 00 00 00 00 00`

`60: 10 00 02 00 e2 8f XX XX XX XX XX XX 12 f4 03 00`

("XX" 是他们不关心的字节) 另一种可能已实施也可能未实施的检测形式,可能会阻止你的固件,即读取你的设备历史记录,可以通过遵循[这篇](https://dma.lystic.dev/anticheat-evasion/clearing-device-history)帖子来清除它。 ### 刷写故障排除 - 如果你弄乱了 CFW 并且你的游戏 PC 无法完全“启动”,无论是由于 bios 挂起还是其他原因,如果卡仍然通电(通常由 LED 指示),你将能够从第二台计算机向其刷入新固件。如果你的主计算机无法保持通电,你必须购买一个 PCIe 延长线,它允许你为 DMA 卡供电而无需其进行‘通信’ **(不推荐:如果延长线不可用,你可以在计算机完全启动后热插拔 dma 卡,然后刷写卡,但请注意,有罕见的报告称这会导致主板损坏)** - 有些主板根本与某些固件不兼容,在某些情况下,这可以通过制作手动内存映射来解决。 ### “功能失调”固件故障排除 - 如果你的速度测试提示类似 `tiny PCIe algorithm` 的内容,则你在配置空间某处犯了错误。你的卡*仍将*起作用,但读取速度会比应有的慢,这会严重影响性能。 - 将某些函数更改为低于可接受的范围(很可能命名为包含 payload/size/speed 之类的名称)**也**会减慢卡的读取速度。最好的做法是将 max read request/payload sizes 设置为 4KB/最高可用 - 某些主板根本与某些固件不兼容,大多数报告都是在 gigabyte 主板上。 - 有时你的固件允许你的设备工作,但会导致大幅减速,然后如果尝试使用 Arbor 或设备管理器读取它,会导致计算机 BSOD。不幸的是,我不确切知道你需要在哪里出错才会发生这种情况,所以我建议重新制作整个固件。我建议保留一个在你的第二台计算机上能用的稳定固件,以防这种情况发生。 - 制作新 .bin 文件时你的更改没有保存?尝试删除你的 `pcileech_squirrel.runs` 和 `pcileech_squirrel.cached` 文件夹,甚至以每个新固件为单位,制作和使用全新 pcileech-fpga 文件夹的副本作为良好实践 ### 当你读完所有这些后, 如果你有任何问题、固件问题或建议,请随时加入我的 Discord 寻求支持。 [](https://discord.gg/m9zmBwn8Y5) ### 额外致谢 Ulf Frisk 的 [pcileech](https://github.com/ufrisk/pcileech)

Ekknod 的 [custom pcileech config](https://github.com/ekknod/pcileech-wifi)(你也可以以此为起点作为基础!)

Garagedweller 的 [Unknown Cheats 帖子](https://www.unknowncheats.me/forum/anti-cheat-bypass/613135-dma-custom-firmware-guide.html),他最初激发了我制作这个指南的灵感,我也将我对这个话题的兴趣归功于他。 ### 赞助这个项目 如果你觉得本指南对你有帮助,值得金钱捐赠,请随时在这里捐赠:

USDT/trc20: `TDa8PUwAdD9rg84ythjXjN52s8UeaejnFN`

LTC: `MMxWW2n5pTbWoY9EakDaTiQ7HKBJy7sxDh`

或者只是给仓库点个 Star 也有**巨大**帮助 <3

也赞助[让这一切成为可能的那个](https://github.com/ufrisk)

#### 📖为什么要制作本指南? 我不喜欢有些人故意含糊其辞,对信息保密,甚至误导他人,使他们无法自己制作固件,最终只能花费数百美元从其他提供商那里购买无法保证质量的自定义固件。 #### 设备兼容性 本指南使用 squirrel DMA 卡。项目请勿使用 Squirrel 文件夹,而是使用你的 DMA 卡对应的文件夹,该文件夹位于 pcileech-fpga-master 文件夹中。 - 35T: Squirrel - 75T: EnigmaX1 - 100T: ZDMA #### 🔎 定义 __DMA__ : Direct Memory Access(直接内存访问) __TLP__ : Transaction Layer Packet(事务层报文) __DSN__ : Device Serial Number(设备序列号) __DW__ : Double Word | DWORD(双字) __Donor card__ : 供应卡(Donor card),用于获取 ID/配置空间,不会在你的主 PC 上使用(例如 PCIE Wifi 卡) __FPGA__ : Field Programmable Gate Array(现场可编程门阵列) ### ⚠️ 免责声明 - 本指南并不总是更新到圈内的最佳实践,实测时请务必谨慎。

- 本指南___不___详述如何设置软件或更改计算机设置以适配 DMA 卡 - 如果你在阅读完整个指南后仍有不理解的概念,底部有一个 Discord 服务器链接 ### 📑 目录 1. [要求](https://github.com/Silverr12/DMA-FW-Guide#1-requirements) 2. [收集供应卡信息](https://github.com/Silverr12/DMA-FW-Guide#2-gathering-the-donor-information) 3. [初始自定义](https://github.com/Silverr12/DMA-FW-Guide#3-initial-customisation) 4. [Vivado 项目自定义](https://github.com/Silverr12/DMA-FW-Guide#4-vivado-project-customisation) 5. [其他配置空间更改](https://github.com/Silverr12/DMA-CFW-Guide#5-other-config-space-changes) 6. [TLP 模拟](https://github.com/Silverr12/DMA-CFW-Guide#6-tlp-emulation) 7. [中断](https://github.com/Silverr12/DMA-CFW-Guide#7-interrupts) 8. [构建、刷写与测试](https://github.com/Silverr12/DMA-CFW-Guide#7-building-flashing--testing) ## **1. 要求** #### 硬件 - 一张供应卡(下文解释) - 当然还有一张 DMA 卡 #### 软件 - 文本编辑器,本指南使用 [Visual Studio](https://visualstudio.microsoft.com/vs/community/)。 - [Xilinx Vivado](https://www.xilinx.com/support/download.html) 需要注册 AMD 账号才能下载 - [Pcileech-fpga](https://github.com/ufrisk/pcileech-fpga) 自定义固件源码 - [Arbor](https://www.mindshare.com/software/Arbor) 需要注册账号才能下载试用版(14 天)

可以通过删除注册表编辑器中的相应文件夹来延长试用期,但我不能告诉你更多了。 - Arbor 的替代品,[Telescan PE](https://www.teledynelecroy.com/protocolanalyzer/pci-express/telescan-pe-software/resources/analysis-software),这个非常相似且完全免费,但注册需要人工审核,可能需要一点时间。 ## **2. 收集供应卡信息** (使用供应卡将有助于我们稍后进行 TLP 模拟,与设备通信以启动驱动程序从而增加合法性)

由于我的测试和知识有限,接下来的所有示例我将使用网络适配器

(如果你知道自己在做什么并了解其中的细微差别,完全可以跳过购买供应卡这一步,但对于新手我强烈建议这样做,花 20 美元换来一个保证能用的产品,比针对延迟检测波进行特定测试要好得多) 建议使用廉价的硬件来获取 ID,然后将其丢弃。这些用于模拟 DMA 卡。**所以不要获取你电脑中任何现有硬件的 ID 并将其插入固件中。因为很可能在未来,如果现在还没有的话,拥有 2 个 1:1 ID 的设备会被检测并标记** ### 使用 Arbor 转到 Local system(本地系统)选项卡下的 Scan Options(扫描选项),按 Scan/Rescan(扫描/重新扫描),默认选中的值对我们来说已经足够了。 进入 PCI Config(PCI 配置)找到你的网络控制器,在 decode(解码)部分滚动查看,并记录以下内容: #### 下面显示的所有 ID 都是我的,你的可能不一样 1. Device ID(设备 ID)  2. Vendor ID(厂商 ID)  3. Revision ID(版本 ID,显示为 RevID)  4. BAR0 Sizing Value(大小值)(1/2/3/4/5 如果你有的话)  点击它所在的方框查看大小信息  我的大小是 16kb,记录下来 5. Subsystem ID(子系统 ID)  6. DSN(列为 Serial Number Register)  合并你的低位和高位 DSN 寄存器,用于我们在第 3 步中的 DSN 配置 例如,这些是我的值: Serial Number Register (Upper DW): `01 00 00 00`

Serial Number Register (Lower DW): `68 4C E0 00`

以相同的格式合并你的值: Upper DW + Lower DW = `01 00 00 00 68 4C E0 00` ## **3. 初始自定义** 再次由于知识有限,目前我将专注于 pcileech 的 PCIeSquirrel 部分,对于使用其他固件的人表示歉意。 ### 使用 Visual Studio 1. 打开 PCIeSquirrel 文件夹并转到文件 `/PCIeSquirrel/src/pcileech_pcie_cfg_a7.sv`。在此文件中使用 Ctrl+F 搜索 `rw[20]`,该值应该在第 209 行,以找到主中止标志/自动清除状态寄存器。将随后的 0 改为 1。 之前  之后  2. 在同一个文件 `pcileech_pcie_cfg_a7.sv` 中,Ctrl+F 搜索 `rw[127:64]`,应该在第 215 行,找到列为 `rw[127:64] <= 64'h0000000101000A35; // cfg_dsn` 的 DSN 字段,在那里插入你的 Serial Number,格式如 `rw[127:64] <= 64'hXXXXXXXXXXXXXXXX; // cfg_dsn`,保持输入字段 16 个字符的长度,如果你的 DSN 较短,请插入零,如示例图像所示。 之前  之后  这是我的 DSN 如果你的供应卡没有 DSN,你的应该是这样 `rw[127:64] <= 64'h0000000000000000; // +008: cfg_dsn` 4. 继续保存你所做的所有更改 ### 生成 Vivado 文件 1. 打开 Vivado,在顶部菜单的搜索查询中,搜索 tcl console 并点击它。  控制台现在应该在应用程序底部打开。  2. 在 Tcl 控制台中,输入 `pwd` 查看工作目录。它应该看起来像这样 `C:/Users/user/AppData/Roaming/Xilinx/Vivado` 3. cd 到 pcileech-fpga-master 项目文件夹中的 PCIeSquirrel 文件夹。它应该看起来像这样 `C:\Users\user\Desktop\pcileech-fpga-master\PCIeSquirrel`。(桌面是我的项目文件夹所在的位置)

如果尝试 cd 到项目目录时出现错误,请将所有 '\\' 替换为 '/' 4. 打开 PCIeSquirrel 目录后,在 Tcl 控制台中输入 `source vivado_generate_project.tcl -notrace` 并等待它完成 5. 项目生成后,Vivado 应自动打开 `pcileech_squirrel.xpr` 文件。先将其保持打开状态。 ## **4. Vivado 项目自定义** 1. 进入 Vivado 后,导航到 "sources" 框并按如下顺序导航 `pcileech_squirrel_top` > `i_pcileech_pcie_a7 : pcileech_pcie_a7` 然后双击带有黄色方块的文件,标记为 `i_pcie_7x_0 : pcie_7x_0`。  2. 你现在应该在一个名为 "Re-customize IP" 的窗口中,在那里,按下 `IDs` 选项卡并输入你从供应板收集的所有 ID,还要注意 "SubSystem Vendor ID" 与你的 Vendor ID 相同。_(如果你的供应板与网络适配器不同,你可能还需要调整下面 "Class Code" 部分的一些设置。)_  要检查供应卡的 class code,请回到 Arbor > 如有需要则扫描,否则 > PCI config > 将 PCI view 设置为 Linear。你的卡应该以绿色高亮显示。还会有一列名为 **Class** 的标题。将其与你的卡匹配。  3. 同时进入 "BARs" 选项卡并设置你在第 2 步收集的大小值,注意显示的 Hex Value 并不意味着要与你的 bar 地址相同。你无法编辑此值。  我的 bar 大小是 16kb,所以你将其设置为 16kb 如果大小单位不同,请更改大小单位以适应 bar 大小的单位 4. 在右下角按 OK,然后在弹出的新窗口中点击 "Generate" 并等待其完成。

5. 我们将锁定核心,以便当 Vivado 综合 and/or 构建我们的项目时,它不会覆盖某些内容,并允许我们手动编辑一些以前只能通过界面完成的事情,为此,导航到底部框右上 "Tcl Console" 并在其中输入 `set_property is_managed false [get_files pcie_7x_0.xci]`,(为了任何目的在未来解锁它,请使用 `set_property is_managed true [get_files pcie_7x_0.xci]`)。 # **第 5 步和第 6 步** 目前正在研究和修订中,因此尚未完成或定稿。请谨慎行事。 ## **5. 其他配置空间更改** 1. 在 Vivado 中,如图所示导航到 `pcie_7x_0_core_top`,并使用文本编辑器左上角的放大镜搜索这些不同的行,以使它们与你的供应卡匹配  #### - 以下是在手动 Vivado IP 核配置中的变量名称列表,它们对应于我们已经确认**不会**破坏固件的值,你可以更改这些值以匹配你的供应卡,我们能够通过 Arbor 的名称进行匹配。按能力匹配,包括:

- (PM) `PM_CAP_VERSION`, `PM_CAP_D1SUPPORT`,`PM_CAP_AUXCURRENT`, `PM_CSR_NOSOFTRST` - (MSI) `MSI_CAP_64_BIT_ADDR_CAPABLE`, - (PCIe) `PCIE_CAP_DEVICE_PORT_TYPE`, `DEV_CAP_MAX_PAYLOAD_SUPPORTED`, `DEV_CAP_EXT_TAG_SUPPORTED`, `DEV_CAP_ENDPOINT_L0S_LATENCY`, `DEV_CAP_ENDPOINT_L1_LATENCY`, `LINK_CAP_ASPM_SUPPORT`, `LINK_CAP_MAX_LINK_SPEED`, `LINK_CAP_MAX_LINK_WIDTH`, `LINK_CTRL2_TARGET_LINK_SPEED` - 可以在不同文件或我还不知道的 GUI 中更改的字段。

- (PM) `cfg_pmcsr_powerstate` - (PCIe) `corr_err_reporting_en`, `non_fatal_err_reporting_en`, `fatal_err_reporting_en`, `no_snoop_en`, `Link Status2: Current De-emphasis` #### - 还建议更改某些功能的块位置,这可以通过更改以下变量来完成: - Capability NEXT Pointers:`CAPABILITIES_PTR`, `MSI_CAP_NEXTPTR`, `PCIE_CAP_NEXTPTR`, `PM_CAP_NEXTPTR` 和 - Capability Pointers: `MSI_BASE_PTR`, `PCIE_BASE_PTR`, `PM_BASE_PTR` 在默认的 pcileech 固件中,你可以找到:**PM 在 0x40,MSI 在 0x50,PCIe 在 0x60**,示例将把它们更改为 **PCIe 在 0x40,PM 在 0xC8 和 MSI 在 0xD0**,但实际上你可以将它们放在任何位置(例如 PCIe 在 0x80,PM 在 0xD0 和 MSI 在 0x90),因为我们的计算机可以并且会跳过空块,你所要做的就是确保 `NEXTPTR` 连接到下一个功能,如下所述,并注意功能大小,以免它们试图重叠。 - 你需要你的 NEXTPTR 从 0x00 的头部开始按顺序排列,并在配置块中向上增加,例如: - 如果我要将我的功能块更改为 `PCIe: 0x40 | PM: 0xC8 | MSI: 0xD0`,我只需将其关联的 `BASE_PTR` 变量分配为相同的值。始终确保从 0x40 或以上开始,因为我们的头部刚好在它之前结束,并且还要确保你的 base ptrs 总是以 0、4 或 8 结尾,例如 40、44 68。 - 其次,我还必须让我的头部 capability pointer `CAPABILITIES_PTR` 指向 40(默认情况下就是这样),因为在这种情况下它是我们要读取的最低/第一个,然后 `PCIE_CAP_NEXTPTR` 将指向 C8,`PM_CAP_NEXTPTR` 指向 D0,`MSI_CAP_NEXTPTR` 指向 00 以结束它,并且始终确保它是从上到下的顺序,如果你尝试在配置空间中向后指向,你的固件在某些情况下将无法工作。(扩展功能如 AER、DSN、LTR 等如果你决定放入它们也需要此配置。但你不要将常规功能指向它们,因为它们是一个单独的‘集合’,除此之外它们遵循与常规功能相同的指针格式。) ## **6. TLP 模拟** 目前你只更改了静态设备属性。然而,正如你在 Windows 设备管理器中看到的黄色警告标志所示,它们并没有与实际设备驱动程序通信。要模拟实际设备,你必须模拟由原始设备的 BAR 定义的内存区域中存储的值。 你可以使用这个小型 C 程序以有用的 verilog 格式复制内存值和相应的地址: ``` #include

- 你会在 `pcileech_squirrel/pcileech_squirrel.runs/impl_1` 中找到该文件,名为 "pchileech_squirrel_top.bin"

- 按照 [LambdaConcept 官方刷写指南](https://docs.lambdaconcept.com/screamer/programming.html) 中的步骤操作 **提醒:仅适用于 SQUIRREL** 3. 从你的第二台计算机运行 DMA 速度测试工具 (Discord 服务器中有链接和下载) 以验证你的固件是否正常工作并按预期读取。 4. 转储你新固件的配置空间,并与下面显示的 **已知** 签名的 pcileech 默认值进行比较,看看是否过于相似。你绝对应该正确看待某些值相同这一事实,你必须考虑到除了序列号和可能的 bar 地址之外,一种类型的(例如)网络卡的配置空间在所有这些卡中都是相同的。GLHF 这是低端检测系统据称在 PCIe 设备的配置空间中扫描的签名之一: [更多信息在这里](https://dma.lystic.dev/anticheat-evasion/detection-vectors)

`40: 01 48 03 78 08 00 00 00 05 60 80 00 00 00 00 00`

`60: 10 00 02 00 e2 8f XX XX XX XX XX XX 12 f4 03 00`

("XX" 是他们不关心的字节) 另一种可能已实施也可能未实施的检测形式,可能会阻止你的固件,即读取你的设备历史记录,可以通过遵循[这篇](https://dma.lystic.dev/anticheat-evasion/clearing-device-history)帖子来清除它。 ### 刷写故障排除 - 如果你弄乱了 CFW 并且你的游戏 PC 无法完全“启动”,无论是由于 bios 挂起还是其他原因,如果卡仍然通电(通常由 LED 指示),你将能够从第二台计算机向其刷入新固件。如果你的主计算机无法保持通电,你必须购买一个 PCIe 延长线,它允许你为 DMA 卡供电而无需其进行‘通信’ **(不推荐:如果延长线不可用,你可以在计算机完全启动后热插拔 dma 卡,然后刷写卡,但请注意,有罕见的报告称这会导致主板损坏)** - 有些主板根本与某些固件不兼容,在某些情况下,这可以通过制作手动内存映射来解决。 ### “功能失调”固件故障排除 - 如果你的速度测试提示类似 `tiny PCIe algorithm` 的内容,则你在配置空间某处犯了错误。你的卡*仍将*起作用,但读取速度会比应有的慢,这会严重影响性能。 - 将某些函数更改为低于可接受的范围(很可能命名为包含 payload/size/speed 之类的名称)**也**会减慢卡的读取速度。最好的做法是将 max read request/payload sizes 设置为 4KB/最高可用 - 某些主板根本与某些固件不兼容,大多数报告都是在 gigabyte 主板上。 - 有时你的固件允许你的设备工作,但会导致大幅减速,然后如果尝试使用 Arbor 或设备管理器读取它,会导致计算机 BSOD。不幸的是,我不确切知道你需要在哪里出错才会发生这种情况,所以我建议重新制作整个固件。我建议保留一个在你的第二台计算机上能用的稳定固件,以防这种情况发生。 - 制作新 .bin 文件时你的更改没有保存?尝试删除你的 `pcileech_squirrel.runs` 和 `pcileech_squirrel.cached` 文件夹,甚至以每个新固件为单位,制作和使用全新 pcileech-fpga 文件夹的副本作为良好实践 ### 当你读完所有这些后, 如果你有任何问题、固件问题或建议,请随时加入我的 Discord 寻求支持。 [](https://discord.gg/m9zmBwn8Y5) ### 额外致谢 Ulf Frisk 的 [pcileech](https://github.com/ufrisk/pcileech)

Ekknod 的 [custom pcileech config](https://github.com/ekknod/pcileech-wifi)(你也可以以此为起点作为基础!)

Garagedweller 的 [Unknown Cheats 帖子](https://www.unknowncheats.me/forum/anti-cheat-bypass/613135-dma-custom-firmware-guide.html),他最初激发了我制作这个指南的灵感,我也将我对这个话题的兴趣归功于他。 ### 赞助这个项目 如果你觉得本指南对你有帮助,值得金钱捐赠,请随时在这里捐赠:

USDT/trc20: `TDa8PUwAdD9rg84ythjXjN52s8UeaejnFN`

LTC: `MMxWW2n5pTbWoY9EakDaTiQ7HKBJy7sxDh`

或者只是给仓库点个 Star 也有**巨大**帮助 <3

也赞助[让这一切成为可能的那个](https://github.com/ufrisk)

标签:35T, 75T, DMA卡, DMA固件, DMA攻击, EnigmaX1, FPGA开发, PCIe, pcileech, Squirrel, TLP, Vivado, Xilinx, ZDMA, 内存劫持, 固件修改, 固件定制, 实时处理, 数字取证, 游戏作弊, 直接内存访问, 硬件安全, 硬件黑客, 网络安全, 自动化脚本, 配置空间, 隐私保护