tigard-tools/tigard

GitHub: tigard-tools/tigard

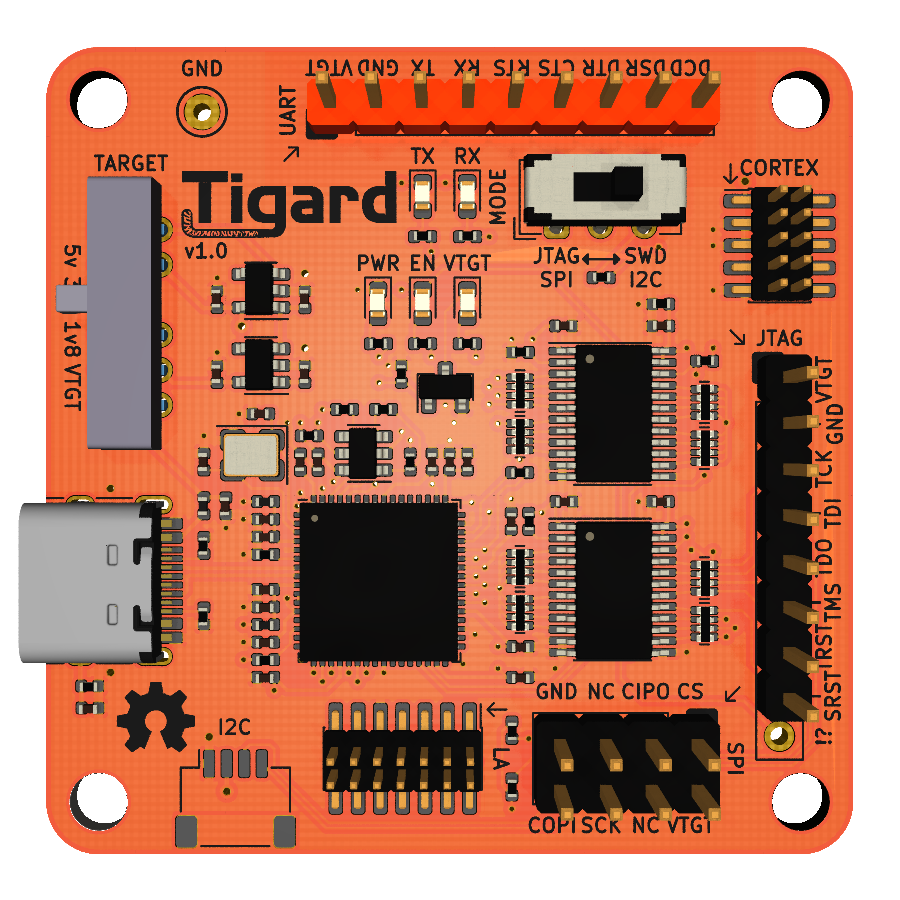

一个基于 FTDI FT2232H 的多协议硬件黑客工具,旨在解决通用调试接口缺失的问题。

Stars: 814 | Forks: 92

# Tigard

一个基于 FTDI FT2232H 的多协议硬件黑客工具。

# 目标

市面上有很多 -232H 系列转接板,但它们通常是针对特定用途设计的,并不是为了方便地连接到各种不同的目标系统。

两个例外是 Exodus Intelligence Hardware Interface Board(不开源且不售卖),以及 [TIMEP](https://github.com/Matir/timep),它是该项目的起源和基础。

# 内容

- [软件功能](#software)

- [硬件功能](#hardware-features)

- [使用说明](#usage)

- [硬件连接](#hardware-hookup)

- [开关](#switches)

- [UART](#uart)

- [SPI](#spi)

- [I2C(在 I2C 或 SPI 引脚头上)](#i2c-on-i2c-spi-or-jtag-header)

- [JTAG 调试(在 JTAG 或 CORTEX 引脚头上)](#jtag-debug-on-jtag-or-cortex-header)

- [JTAG 边界扫描(在 JTAG 或 CORTEX 引脚头上)](#jtag-boundary-scan-on-jtag-or-cortex-header)

- [SWD(在 CORTEX 引脚头上)](#swd-on-cortex-header)

- [iCE40 编程](#ice40-programming)

- [AVR ISP](#avr-isp)

- [调试](#debugging)

- [引脚定义](#pinouts)

- [条纹与尾巴](#stripes-and-tails)

- [外壳(Dens)](#dens)

- [序列号](#serial-numbers)

- [获取 Tigard](#getting-tigard)

# 软件功能

Tigard 设计为开箱即用,兼容多个已经支持 x232H 系列芯片的工具和库,包括:

* UART 的 USB-Serial 驱动

* 用于 JTAG 的 OpenOCD 和 URJTAG

* 用于 SPI 接口的 Flashrom、libmpsse、pyftdi 等工具

* 用于 I2C 接口的 libmpsse 和 pyftdi

* 用于 ice40 FPGA 的 iceprog

* 用于 AVR 微控制器的 avrdude

此外,用户也使用 Tigard 与 [BMDA](/../../issues/66)、[Mitou jtag](/../../issues/79)、[VSCode](/../../pull/75) 和 [SPI via FTDI](/../../issues/40) 配合。

# 硬件功能

亮点:

* 双端口设计:一个端口专用于 UART,另一个端口与其他接口共享

* 高性能方向电平转换器,支持 1.8 到 5.5V 电平

* 电压选择开关,可在板载 1.8、3.3、5.0V 供电与 vTarget 之间切换

* 模式选择开关,可在 SPI/JTAG 与 I2C/SWD 模式之间切换

* 逻辑分析仪端口,用于观察设备级信号(v1.0 及之后版本)

* 指示灯,辅助调试

# 使用说明

## 硬件连接

从板子完全断开开始:

1. 使用夹子或跳线将板子连接到目标系统

2. 选择正确的模式(SPI/JTAG 或 SWD/I2C)

3. 确保电压开关处于 VTGT 模式

4. 插入 USB 电缆。PWR 和 EN 指示灯将亮起

5. 给目标设备上电

6. 如果将 VTGT 连接到目标,VTGT 指示灯会亮起;否则可以用电压选择开关选择电压

## 开关

Tigard 上有两个开关用于设置工作模式:一个控制电压,一个控制多个 IO 引脚的布线方式。两者都需要为特定模式正确设置。具体细节请参见各接口章节,但以下是模式摘要:

#### 电压开关

该开关选择电平转换器和目标系统的参考电压:

* 1V8、3V3 和 5V 都会向 VTGT 引脚施加电压

* VTGT 断开与供电的关联,依赖连接到目标的线缆来设置电平转换器电压

这会产生三种使用场景:

1. **目标供电**:将开关设为 VTGT,并将 VTGT 线缆连接到**已供电**的目标。此时目标为电平转换器供电。

2. **Tigard 供电**:将开关设为某一电压,并将 VTGT 连接到**未供电**的目标。此时 Tigard 向目标供电。

3. **自供电**:将开关设为某一电压,但**不连接** VTGT 线缆。Tigard 自身为电平转换器供电,目标自行供电。

#### 模式开关

该开关控制部分 IO 引脚的连接方式,用于特定用途:

* 设为 JTAG/SPI 模式时:

* 所有信号直通

* CORTEX 和 JTAG 引脚头配置为标准 JTAG

* SPI/JTAG 引脚头可用于 SPI

* 设为 SWD/I2C 模式时:

* DO 和 DI 连接在一起,形成 SWDIO 或 SDA

* CORTEX 和 JTAG 引脚头可用于 SWD

* SPI/JTAG 引脚头可用于 I2C

## UART

#### 连接

* 大多数情况下需要 UART 引脚头的 2、3、4 号引脚——GND、TX 和 RX。将它们连接到目标

* 如果目标有 VCC 引脚头,将 1 号引脚 VTGT 连接到它,并将电压选择器设为 VTGT

* 如果没有 VCC 引脚头,断开 VTGT 线缆,并使用选择器设置目标电压

#### 软件

两个串口中的第一个连接到 UART 引脚头。插入 Tigard 后,会出现两个串口设备——第一个即为目标串口。在软件中使用对应的串口,例如:

```

screen /dev/ttyUSB0 115200

```

## SPI

#### 连接

SPI/I2C 引脚头的布局与标准 8 引脚 SPI 闪存芯片一致,便于使用夹子或插座连接。

* 在模式开关上选择 SPI/JTAG

* 将夹子或插座连接到引脚头。注意 1 号引脚,通常插座上会有标记,或排线上的红色/高亮线

* 将夹子连接到目标或将芯片插入插座

* 如果是电路内连接,**必须**采取额外措施,确保没有其他设备与 SPI 设备通信

* 如果在目标供电状态下使用夹子,请将电压选择器设为 VTGT 选项

* 如果使用不带电目标的 ZIF 插座或夹子,请在电压选择器上设置相应电压

#### 软件

Flashrom 是最常用的 SPI 闪存转储工具。但尽管普及,它速度很慢且效率不高。

```

flashrom -p ft2232_spi:type=2232H,port=B,divisor=4

```

libmpsse 是用于控制 MPSSE 或 x232H 系列高速串口的强大库。但由于依赖较多,已不再推荐使用。

pyftdi 是一个新的、简单的接口,与 libmpsse 非常相似:

```

from pyftdi.ftdi import Ftdi

Ftdi.show_devices()

from os import environ

ftdi_url = environ.get('FTDI_DEVICE', 'ftdi://ftdi:2232:1:23f/2')

from spiflash.serialflash import SerialFlashManager

flash=SerialFlashManager.get_flash_device(ftdi_url)

print("Flash device: %s @ SPI freq %0.1f MHz" % (flash, flash.spi_frequency/1E6))

f=open("data.bin","wb")

f.write(flash.read(0,len(flash)))

f.close()

```

## I2C(在 I2C、SPI 或 JTAG 引脚头上)

#### 连接

I2C 引脚头(硬件版本 1.0 及之后)与 [Sparkfun 的 Qwiic](https://www.sparkfun.com/qwiic) 和 [Adafruit 的 STEMMA QT](https://learn.adafruit.com/introducing-adafruit-stemma-qt/what-is-stemma-qt) 系统兼容:

* 将 4 针 JST SH 兼容电缆插入 I2C 连接器

* 将另一端连接到你的 STEMMA QT、Qwiic 或其他 I2C 设备

此外,SPI 引脚头的布局与大多数 8 引脚 I2C 芯片一致,便于使用夹子或插座:

* 将夹子或插座连接到引脚头。注意 1 号引脚,通常插座上会有标记,或排线上的红色/高亮线

* 将夹子连接到目标或将芯片插入插座

最后,JTAG 引脚头也可以用来获取 .1 英寸的独立 I2C 信号:

* 将 8 线 JTAG 线缆连接到 JTAG 连接器

* 将白色 SCL 和灰色 SDA 线缆连接到目标的 I2C 引脚

无论哪种情况,都需要正确设置 Tigard 的开关:

* 在模式选择开关上选择 I2C

* 如果连接在电路中的目标设备有电源,选择 VTGT 选项

* 如果连接的是独立传感器、带电关闭的插座或夹子,请在电压选择器上选择正确电压

#### 特殊情况

FT2232H 的 I2C 实现非常有限。I2C 依赖开漏/开集电极而非推挽三态 I/O,但 FT2232H 支持不佳。因此:

*仅支持控制器模式,不支持设备模式

* 如果 I2C 总线上有其他控制器,Tigard 可能无法正常工作

* 不支持时钟拉伸

* I2C 开关将 DI 和 DO 线短接,以实现双向通信

* 未包含上拉电阻,因为它们通常位于目标板上,而电平转换器上的弱上拉已足够

#### 扩展技巧

为了兼容 I2C 和 SWD,DI 和 DO 通过电阻 R16 合并。这是 SWD 所必需的,通常对 I2C 也可接受。

许多 I2C 目标已有上拉电阻。此外,Tigard 的所有 IO 引脚都有弱 100K 上拉。在测试中,这对大多数 I2C 设备的电路内和外部使用已足够。如果需要更强的上拉,可以临时通过拉高 SPI 引脚的 COPI 和 SCK,或 JTAG 引脚的 TCK 和 TDI 来实现。

#### 软件

libmpsse 是用于控制 MPSSE 或 x232H 系列高速串口的强大库。但由于依赖较多,已不再推荐使用。

pyftdi 是一个新的、简单的接口,与 libmpsse 非常相似:

```

from pyftdi.ftdi import Ftdi

Ftdi.show_devices()

from os import environ

ftdi_url = environ.get('FTDI_DEVICE', 'ftdi://ftdi:2232:1:23f/2')

from i2cflash.serialeeprom import SerialEepromManager

flash = SerialEepromManager.get_flash_device(ftdi_url,'24AA32A',0x50)

flash.write(5,10)

flash.read(0,32)

```

## JTAG 调试(在 JTAG 或 CORTEX 引脚头上)

#### 连接

JTAG 引脚头的布局与 FTDI I/O 引脚标签顺序一致,以与许多 x232H breakout 板保持一致。

此外,CORTEX 引脚头也按标准 ARM 10 针 JTAG 引脚布线。

请务必将模式开关设为 JTAG。这会确保 TDI 和 TDO 分离,并保证 TMS 正确布线到 CORTEX 引脚头。否则,将使用标准连接方式。

#### 软件

**注意:这些 OpenOCD 配置需要 OpenOCD v0.12+**。早期版本可能使用在此提交中更新的已弃用命令:https://github.com/tigard-tools/tigard/commit/5e5722944c8c1ec73b0fa85d574793300c23b3ce

OpenOCD 是用于 ARM、MIPS 等架构的在芯片调试的强大工具。

对应的配置文件(请将其设为链接文件)应如下所示:

```

adapter driver ftdi

transport select jtag

ftdi vid_pid 0x0403 0x6010

ftdi channel 1

adapter speed 2000

ftdi layout_init 0x0038 0x003b

ftdi layout_signal nTRST -data 0x0010

ftdi layout_signal nSRST -data 0x0020

```

在 openocd 中使用:

```

openocd -f tigard-jtag.cfg

```

## JTAG 边界扫描(在 JTAG 或 CORTEX 引脚头上)

边界扫描可用于控制设备以设置 I/O 引脚状态(`EXTEST`),或在设备运行期间查看其状态(`SAMPLE`)。

#### 连接

连接方式与 [JTAG 调试(JTAG 或 CORTEX 引脚头)](#jtag-debug-on-jtag-or-cortex-header) 中所述相同。

引脚布局与运行在 `B` 接口上的 `Olimex ARM-USB-OCD` 兼容。

#### 软件

[UrJTAG](https://urjtag.sourceforge.io/) 是面向底层和边界扫描使用的开源 JTAG 控制软件。

需要告知 UrJTAG Tigard 的 VID 和 PID,以及 JTAG 位于接口 1(默认是 0)。由于一个 bug,TCK 的计算值可能偏高 5 倍——例如下面设置中实际为 500kHz。

[TopJTAG](http://www.topjtag.com/) 是一个更易用但商业($100)且仅限 Windows 的选项。它包含一个“波形视图”,允许你在设备运行时查看任意引脚状态,如同设备上连接了逻辑分析仪。使用 TopJTAG 时,将以下作为 JTAG 连接设置:

* `Connection`:Generic FTDI FT2232

* `Device`:Tigard V1.0 B

* `Static Pins`:Olimex ARM-USB-OCD

* `TCK Freq`:2 MHz(按需调整)

一个支持 Tigard 的开源选项是 [JTAG Boundary Scanner](https://github.com/viveris/jtag-boundary-scanner),它提供 Windows GUI,但后端库是跨平台的(用 C 编写)。该库提供许多功能,例如能够与连接到目标芯片的 SPI 设备通信(警告——速度较慢!)。

该库的 Python 绑定 Alpha 版本可在 [PyJTAGBS](https://github.com/colinoflynn/pyjtagbs) 中获取。例如使用 Tigard 检查扫描链:

```

from jtagbs import JTAGCore, JTAGBS

interface = JTAGCore()

jtag = JTAGBS(interface)

probes = jtag.list_available_probes()

print(probes)

jtag.open_probe('Tigard V1.0 B')

jtag.init_scanchain()

print(jtag.list_devids())

```

有关加载用于切换特定引脚的 BSDL 文件的更多示例,请参见 PyJTAGBS 文档。如果驱动加载正确,应使用的探针名称为 `'Tigard V1.0 A TG100065A'` 和 `'Tigard V1.0 B TG100065B'`。

## SWD(在 CORTEX 引脚头上)

#### 连接

SWD 引脚头是一个标准的 10 针引脚头,常见于许多 SWD 目标开发板。使用两端带有相同引脚头的短“SWD”电缆是连接大多数目标的最佳方式。

请务必将模式开关设为 SWD。这将使用电阻 R16 将 DI 和 DO 连接起来,形成双向 SWDIO 引脚,并连接到 CORTEX 引脚头的 2 号引脚。否则,将使用标准连接方式。

#### 软件

**注意:这些 OpenOCD 配置需要 OpenOCD v0.12+**。早期版本可能使用在此提交中更新的已弃用命令:https://github.com/tigard-tools/tigard/commit/5e5722944c8c1ec73b0fa85d574793300c23b3ce

OpenOCD 是用于 ARM、MIPS 等架构的在芯片调试的强大工具。要在 Tigard 上使用 SWD,需要从源码构建它。AND!XOR DC27 Badge 的 [逐步说明](https://hackaday.io/project/164346-andxor-dc27-badge/log/166464-swd-all-the-things) 涵盖了完整流程。

对应的配置文件(请将其设为链接文件)应如下所示:

```

adapter driver ftdi

transport select swd

ftdi vid_pid 0x0403 0x6010

ftdi channel 1

adapter speed 2000

ftdi layout_init 0x0028 0x002b

ftdi layout_signal SWD_EN -data 0

ftdi layout_signal nSRST -data 0x0020

```

在 openocd 中使用:

```

openocd -f tigard-swd.cfg

```

## iCE40 编程

Lattice iCE40 系列 FPGA 因其低成本和开源工具链而适用于小型项目。虽然这是非常特定的目标,但 Tigard 拥有所有必要的引脚,非常适合编程设备。

#### 连接

所有必要引脚都在 JTAG 引脚头上。

默认未安装“!?”引脚。JTAG 的“!?”引脚与 UART RX 引脚在内部短路,以防你需要刷新 iCE40 但不想焊接 Tigard。详见下表。

请务必在模式选择开关上选择 JTAG/SPI。这会确保 COPI 和 CIPO 分离。

如果计划编程 SRAM 而非 FLASH:

* 交换 COPI 和 CIPO

* 断开 CS 与 FLASH 的连接,但保留其连接到 iCE40

#### 软件

要编程目标的非易失 FLASH,请使用 iceprog:

```

iceprog -I B yourbitstream.bin

```

如果希望直接编程 ice40 的 SRAM,请确保调整布线并再次使用 iceprog:

```

iceprog -I B -S yourbitstream.bin

```

请注意,如果选择编程 SRAM,位流将在断电后丢失。

## AVR ISP

要编程包括许多 Arduino 开发板在内的 AVR 微控制器,请使用带有自定义配置文件的 avrdude。

#### 连接

请务必在模式选择开关上选择 JTAG/SPI。使用 SRST 作为复位信号。

#### 软件

Avrdude 是一个开源的 AVR 烧录工具。Avrdude 7.1 及更高版本已内置对 Tigard 的支持——你只需:

```

avrdude -c tigard

```

对于旧版本,请创建以下 `tigard.conf` 文件,以便将 Tigard 识别为 avrftdi 兼容设备并指定使用的引脚:

```

programmer

parent "avrftdi"

id = "tigard";

desc = "Tigard interface board";

usbdev = "B";

sck = 0;

mosi = 1;

miso = 2;

reset = 5;

;

```

然后,使用 `-C +tigard.conf` 添加配置文件,并使用 `-c tigard` 指定编程器:

```

avrdude -C +tigard.conf -c tigard

```

# 调试

#### PWR 指示灯:

当板子有 USB 供电时该灯会亮起;插入 USB 电缆后应立即点亮。

* 如果不亮,请检查 USB 线缆和电源。

* 如果灯亮后熄灭、变暗或闪烁,很可能线缆或目标存在短路。

#### EN 指示灯:

当 FTDI 芯片正常工作时该灯会亮起,通常在 USB 供电灯亮起后稍亮。

* 如果不亮,可能是 USB 线缆故障、仅供电的 USB 端口/线缆或 FTDI 芯片损坏。

#### VTGT 指示灯:

当电平转换器正常供电时该灯会亮起,无论是由目标供电还是由板载电平选择器供电。

* 如果在 VTGT 模式下不亮,请检查目标供电及与目标的电源和地线连接。

* 如果选择了电压但灯不亮,很可能线缆或目标存在短路。

* 存在某些边界情况,VTGT 可能被[锁存到输出引脚施加的电压](https://github.com/tigard-tools/tigard/issues/20)。养成始终从 VTGT 关闭开始使用的习惯有助于避免此问题。

#### 所有指示灯全亮:

当所有灯都亮起时igard 很可能按预期工作。如果仍有问题,可能性如下(按可能性从高到低排列):

* 是**接线问题**。请确保线缆连接良好,并用万用表确认。

* 是**目标问题**。尝试更换目标以确认软件是否正常工作。

* 是**软件问题**。尝试更换软件工具或模式以确认板子是否正常工作。

* 是**协议问题**。使用逻辑分析仪或示波器观察信号是否正确。

* 是**硬件问题**。尝试更换另一块 Tigard 板。

* 是**Tigard 问题**。尝试更换另一块 x232H 开发板。

# 引脚定义

引脚定义的选择基于易用性原则,具体包括:

* 如果存在广泛使用的标准,优先采用(SWD)

* 如果存在主要的主流用途,采用该方式(SPI/I2C)

* 如果其他常见开发板有对应引脚定义,采用其定义(UART 和 JTAG)

### UART

2.54mm 间距,1x9 针排针。

该引脚定义优先将 FT2232H 引脚按顺序排列——类似于许多 x232H breakout 板。

VTGT、GND、TX、RX 的颜色与大多数 USB-Serial 线缆一致。其余引脚包含但未安装在引脚头上,用户可根据需要选装。

| 引脚编号 | UART 信号 | 颜色 | FT2232H 引脚 |

|----------|-----------|------|--------------|

| 1 | VTGT | 红色 | -- |

| 2 | GDD | 黑色 | -- |

| 3 | TX | 绿色 | AD0 |

| 4 | RX | 白色 | AD1 |

| 5 | RTS | -- | AD2 |

| 6 | CTS | -- | AD3 |

| 7 | DTR | -- | AD4 |

| 8 | DSR | -- | AD5 |

| 9 | DCD | -- | AD6 |

### SWD

1.27mm 间距,2x5 针排针。

这是标准引脚定义。为了兼容 SWD 和 JTAG,模式开关:

1. 将 DI 和 DO 合并为 SWDIO

2. 选择引脚 2 为 SWDIO 或 TMS

| 引脚编号 | SWD 信号 | FT2232H 引脚 | JTAG 信号 | FT2232H 引脚 |

|----------|----------|--------------|-----------|--------------|

| 1 | VTGT | -- | VTGT | -- |

| 2 | SWDIO | BD1 BD2 | TMS | BD3 |

| 3 | GND | -- | GND | -- |

| 4 | SWDCLK | BD0 | TCK | BD0 |

| 5 | GND | -- | GND | -- |

| 6 | NC | -- | TDO | BD2 |

| 7 | KEY | -- | KEY | -- |

| 8 | NC | -- | TDI | BD1 |

| 9 | GND | -- | GND | -- |

| 10 | nSRST | BD5 | nSRST | BD5 |

### JTAG

2.54mm 间距,1x8 针排针。

该引脚定义优先将 FT2232H 引脚按顺序排列——类似于许多 x232H breakout 板。

一般使用时请将模式开关设为 SPI/JTAG 模式。

线缆颜色参考 [SecuringHardware.com](https://SecuringHardware.com/) 使用的 Adafruit FT232H 线缆颜色方案,颜色选择是因为逻辑分析课堂常使用黑、棕、红、橙,因此为线缆选择了这些独特颜色。

该引脚头也可用于 I2C 和 SPI(如果 8 针定义不适用)。

| 引脚编号 | JTAG 引脚 | 颜色 | FT2232H 引脚 |

|----------|-----------|-------|--------------|

| 1 | VTGT | 红色 | -- |

| 2 | GND | 黑色 | -- |

| 3 | TCK | 白色 | BD0 |

| 4 | TDI | 灰色 | BD1 |

| 5 | TDO | 紫色 | BD2 |

| 6 | TMS | 蓝色 | BD3 |

| 7 | TRST | 绿色 | BD4 |

| 8 | SRST | 黄色 | BD5 |

### SPI

2.54mm 间距,2x4 针排针。

该引脚定义专门匹配大多数 8 引脚 SPI 和 I2C 芯片的引脚布局,便于使用夹子或插座连接。

为了兼容 SPI 和 I2C,模式开关:

1. 将 DI 和 DO 合并为 SDA(I2C 模式)

2. 在 I2C 模式下断开引脚 2(用于设备地址信号)

| 芯片引脚编号 | 引脚头编号 | SPI 信号 | FT2232H 引脚 |

|--------------|------------|----------|--------------|

| 1 | 1 | CS | BD3 |

| 2 | 3 | CIPO | BD2 |

| 3 | 5 | WP | 上拉 |

| 4 | 7 | GND | -- |

| 5 | 8 | COPI | BD1 |

| 6 | 6 | SCK | BD0 |

| 7 | 4 | EN | 上拉 |

| 8 | 2 | VTGT | -- |

### LA

1.27mm 间距,2x7 针排针。

LA 端口便于将逻辑分析仪连接到 Tigard 与目标硬件之间的信号,便于监控 UART、SPI 和 JTAG,也通常适用于 I2C。

虽然可以使用 FT2232H 作为简易逻辑分析仪,但这不是设计初衷——预期使用场景是:Tigard 与目标通信,但需借助外部逻辑分析仪调试通信过程。

LA 端口可作为被动机械适配器使用([不支持](https://github.com/tigard-tools/tigard/issues/20))。为获得最佳效果,请给 Tigard 供电但断开 VTGT 与目标的连接,并注意信号完整性。

该端口设计用于直接连接 Bitmagic 逻辑分析仪,或使用 Bitmagic 线缆连接其他工具。

8 个最关键的信号已连接——6 个来自 JTAG/SWD/SPI/I2C 端口,2 个来自 UART 端口。

| 引脚编号 | Bitmagic 信号 | FT2232 引脚 | JTAG 信号 | SPI 信号 | SWD 信号 | I2C 信号 | UART 信号 |

|----------|---------------|-------------|-----------|----------|----------|----------|-----------|

| 1 | xPB0 | BD0 | TCK | SCK | SWCLK | SCL | |

| 2 | xPB1 | BD1 | TDI | COPI | SWDIO | SDA | |

| 3 | xPB2 | BD2 | TDO | CIPO | SWDIO | SDA | |

| 4 | xPB3 | BD3 | TMS | CS | | | |

| 5 | xPB4 | BD4 | TRST | | | | |

| 6 | xPB5 | BD5 | SRST | | | | |

| 7 | xPB6 | AD0 | | | | | TX |

| 8 | xPB7 | AD1 | | | | | RX |

| 9 | GND | | | | | | |

| 10 GND | | | | | | |

| 11 | xTRIG | | | | | | |

| 12 | xCLK | | | | | | |

| 13 | xTRIG2 | | | | | | |

| 14 | xIFCLK | | | | | | |

### I2C

1mm 间距,1x4 针排针,JST SH 兼容。

该引脚定义专门匹配 [Sparkfun 的 Qwiic](https://www.sparkfun.com/qwiic) 和 [Adafruit 的 STEMMA QT](https://learn.adafruit.com/introducing-adafruit-stemma-qt/what-is-stemma-qt) 系统。

使用模式开关选择 I2C/SWD 模式。

| 引脚编号 | I2C 信号 | FT2232H 引脚 |

|----------|----------|--------------|

| 1 | GND | --- |

| 2 | VCC | --- |

| 3 | SDA | BD1 和 BD2 |

| 4 | SCL | BD0 |

### iCE40

使用 JTAG 引脚头,并额外使用未占用的“!?”引脚。

| 引脚编号 | 标签 | iCE40 信号 | FT2232 引脚 |

|----------|-------------|--------------|--------------|

| 1 | VTGT | VTGT | --- |

| 2 | GND | GND | --- |

| 3 | TCK | CLK | BD0 |

| 4 | TDI/MOSI/SDA| MOSI/COPI | BD1 |

| 5 | TDO/MISO/-- | MISO/CIPO | BD2 |

| 6 | TMS/SS/-- | --- | --- |

| 7 | TRST/CS/ICE_SS_B | CS/ICE_SS_B | BD4 |

| 8 | SRST/CRESET | RESET | BD5 |

| 9 | !? | CDONE | BD6 |

JTAG 的“!?”引脚与 UART RX 引脚内部短路,以便在不焊接 Tigard 的情况下刷新 iCE40。

### AVR ISP

常见于 AVR 开发板的 6 针 ICSP 引脚头需要以下连接:

| 引脚编号 | 标签 | ISP 信号 | ICSP 引脚 | FT2232 引脚 |

|----------|-------------|----------|-----------|--------------|

| 1 | VTGT | VTGT | 2 | --- |

| 2 | GND | GND | 6 | --- |

| 3 | TCK | SCK | 3 | BD0 |

| 4 | TDI/MOSI/SDA| MOSI | 4 | BD1 |

| 5 | TDO/MISO/-- | MISO | 1 | BD2 |

| 6 | TMS/SS/-- | --- | --- | --- |

| 7 | TRST/-- | --- | --- | --- |

| 8 | SRST/RST | RST | 5 | BD5 |

# 条纹与尾巴

为了支持不同接口,可以使用定制布线或扩展板。推荐名称:“Tigard Stripes”指扩展板,“Tigard Tails”指布线。

* `UART Tail` 随板附带,包含 VTGT、GND、TX 和 RX

* `JTAG Tail` 随板附带,包含标好的多用途 JTAG、SPI 和 I2C 信号线

* `SOIC8 Tail` 指带排缆的廉价 SOIC-8 夹具,兼容 SPI/I2C 引脚头

# Dens(外壳)

Tigard 以裸板形式提供,但有多种 3D 打印的安装座和外壳(“Dens”)可供选择:

* 第一个 [TigarDen](https://github.com/hamid-elaosta/TigarDen) 由 hamid 设计,是用于固定 Tigard 的多件式上下外壳

* [底部外壳](https://www.thingiverse.com/thing:5166570) 由 phaktor 设计,底部有漂亮的虎纹,或可单色打印

* [带铰链的外壳](https://www.thingiverse.com/thing:5169952) 由 professor_plum 设计,可容纳 Tigard、Bitmagic 和多个探针

* [简化 2 件式外壳](https://cad.onshape.com/documents/832906f0b96360664fedfe62/w/f1b917fd93e5b559c0927cf4/e/eb5666e6e328afd821567f83) 由 jwise 设计,适用于铣削或打印

* [tigard-tray](https://github.com/tigard-tools/tigard-tray) 是一个 3D 打印托盘,可固定 Tigard、Bitmagic 和 9 个探针夹,同时保护引脚,便于在拉链包中滑动

# 序列号

Tigard 遵循序列号分配约定。如果你决定自行制作并销售 Tigard,请将前两个字符 “TG” 替换为其他内容。

格式:`TGMmxxxx`

* `TG` — 固定标识,表示 “Tigard”

* `M` — 主版本号(十进制)

* `m` — 次版本号(十进制)

* `xxxx` — 4 位小写十六进制序列号,从 0 开始补零

## 已分配

* 第一批 28 个(2020 年 7 月 5 日):TG010000 - TG01001b

* 第二批 42 个(2020 年 8 月 5 日):TG01001c - TG010046

* 第三批 496 个(2020 年 10 月):TG100000 - TG1001f0

* 第四批 693 个(2021 年 1 月):TG110000 - TG1102b5

* 第四批 697 个(2021 年 9 月):TG110400 - TG1106b9

# Tigard

一个基于 FTDI FT2232H 的多协议硬件黑客工具。

# 目标

市面上有很多 -232H 系列转接板,但它们通常是针对特定用途设计的,并不是为了方便地连接到各种不同的目标系统。

两个例外是 Exodus Intelligence Hardware Interface Board(不开源且不售卖),以及 [TIMEP](https://github.com/Matir/timep),它是该项目的起源和基础。

# 内容

- [软件功能](#software)

- [硬件功能](#hardware-features)

- [使用说明](#usage)

- [硬件连接](#hardware-hookup)

- [开关](#switches)

- [UART](#uart)

- [SPI](#spi)

- [I2C(在 I2C 或 SPI 引脚头上)](#i2c-on-i2c-spi-or-jtag-header)

- [JTAG 调试(在 JTAG 或 CORTEX 引脚头上)](#jtag-debug-on-jtag-or-cortex-header)

- [JTAG 边界扫描(在 JTAG 或 CORTEX 引脚头上)](#jtag-boundary-scan-on-jtag-or-cortex-header)

- [SWD(在 CORTEX 引脚头上)](#swd-on-cortex-header)

- [iCE40 编程](#ice40-programming)

- [AVR ISP](#avr-isp)

- [调试](#debugging)

- [引脚定义](#pinouts)

- [条纹与尾巴](#stripes-and-tails)

- [外壳(Dens)](#dens)

- [序列号](#serial-numbers)

- [获取 Tigard](#getting-tigard)

# 软件功能

Tigard 设计为开箱即用,兼容多个已经支持 x232H 系列芯片的工具和库,包括:

* UART 的 USB-Serial 驱动

* 用于 JTAG 的 OpenOCD 和 URJTAG

* 用于 SPI 接口的 Flashrom、libmpsse、pyftdi 等工具

* 用于 I2C 接口的 libmpsse 和 pyftdi

* 用于 ice40 FPGA 的 iceprog

* 用于 AVR 微控制器的 avrdude

此外,用户也使用 Tigard 与 [BMDA](/../../issues/66)、[Mitou jtag](/../../issues/79)、[VSCode](/../../pull/75) 和 [SPI via FTDI](/../../issues/40) 配合。

# 硬件功能

亮点:

* 双端口设计:一个端口专用于 UART,另一个端口与其他接口共享

* 高性能方向电平转换器,支持 1.8 到 5.5V 电平

* 电压选择开关,可在板载 1.8、3.3、5.0V 供电与 vTarget 之间切换

* 模式选择开关,可在 SPI/JTAG 与 I2C/SWD 模式之间切换

* 逻辑分析仪端口,用于观察设备级信号(v1.0 及之后版本)

* 指示灯,辅助调试

# 使用说明

## 硬件连接

从板子完全断开开始:

1. 使用夹子或跳线将板子连接到目标系统

2. 选择正确的模式(SPI/JTAG 或 SWD/I2C)

3. 确保电压开关处于 VTGT 模式

4. 插入 USB 电缆。PWR 和 EN 指示灯将亮起

5. 给目标设备上电

6. 如果将 VTGT 连接到目标,VTGT 指示灯会亮起;否则可以用电压选择开关选择电压

## 开关

Tigard 上有两个开关用于设置工作模式:一个控制电压,一个控制多个 IO 引脚的布线方式。两者都需要为特定模式正确设置。具体细节请参见各接口章节,但以下是模式摘要:

#### 电压开关

该开关选择电平转换器和目标系统的参考电压:

* 1V8、3V3 和 5V 都会向 VTGT 引脚施加电压

* VTGT 断开与供电的关联,依赖连接到目标的线缆来设置电平转换器电压

这会产生三种使用场景:

1. **目标供电**:将开关设为 VTGT,并将 VTGT 线缆连接到**已供电**的目标。此时目标为电平转换器供电。

2. **Tigard 供电**:将开关设为某一电压,并将 VTGT 连接到**未供电**的目标。此时 Tigard 向目标供电。

3. **自供电**:将开关设为某一电压,但**不连接** VTGT 线缆。Tigard 自身为电平转换器供电,目标自行供电。

#### 模式开关

该开关控制部分 IO 引脚的连接方式,用于特定用途:

* 设为 JTAG/SPI 模式时:

* 所有信号直通

* CORTEX 和 JTAG 引脚头配置为标准 JTAG

* SPI/JTAG 引脚头可用于 SPI

* 设为 SWD/I2C 模式时:

* DO 和 DI 连接在一起,形成 SWDIO 或 SDA

* CORTEX 和 JTAG 引脚头可用于 SWD

* SPI/JTAG 引脚头可用于 I2C

## UART

#### 连接

* 大多数情况下需要 UART 引脚头的 2、3、4 号引脚——GND、TX 和 RX。将它们连接到目标

* 如果目标有 VCC 引脚头,将 1 号引脚 VTGT 连接到它,并将电压选择器设为 VTGT

* 如果没有 VCC 引脚头,断开 VTGT 线缆,并使用选择器设置目标电压

#### 软件

两个串口中的第一个连接到 UART 引脚头。插入 Tigard 后,会出现两个串口设备——第一个即为目标串口。在软件中使用对应的串口,例如:

```

screen /dev/ttyUSB0 115200

```

## SPI

#### 连接

SPI/I2C 引脚头的布局与标准 8 引脚 SPI 闪存芯片一致,便于使用夹子或插座连接。

* 在模式开关上选择 SPI/JTAG

* 将夹子或插座连接到引脚头。注意 1 号引脚,通常插座上会有标记,或排线上的红色/高亮线

* 将夹子连接到目标或将芯片插入插座

* 如果是电路内连接,**必须**采取额外措施,确保没有其他设备与 SPI 设备通信

* 如果在目标供电状态下使用夹子,请将电压选择器设为 VTGT 选项

* 如果使用不带电目标的 ZIF 插座或夹子,请在电压选择器上设置相应电压

#### 软件

Flashrom 是最常用的 SPI 闪存转储工具。但尽管普及,它速度很慢且效率不高。

```

flashrom -p ft2232_spi:type=2232H,port=B,divisor=4

```

libmpsse 是用于控制 MPSSE 或 x232H 系列高速串口的强大库。但由于依赖较多,已不再推荐使用。

pyftdi 是一个新的、简单的接口,与 libmpsse 非常相似:

```

from pyftdi.ftdi import Ftdi

Ftdi.show_devices()

from os import environ

ftdi_url = environ.get('FTDI_DEVICE', 'ftdi://ftdi:2232:1:23f/2')

from spiflash.serialflash import SerialFlashManager

flash=SerialFlashManager.get_flash_device(ftdi_url)

print("Flash device: %s @ SPI freq %0.1f MHz" % (flash, flash.spi_frequency/1E6))

f=open("data.bin","wb")

f.write(flash.read(0,len(flash)))

f.close()

```

## I2C(在 I2C、SPI 或 JTAG 引脚头上)

#### 连接

I2C 引脚头(硬件版本 1.0 及之后)与 [Sparkfun 的 Qwiic](https://www.sparkfun.com/qwiic) 和 [Adafruit 的 STEMMA QT](https://learn.adafruit.com/introducing-adafruit-stemma-qt/what-is-stemma-qt) 系统兼容:

* 将 4 针 JST SH 兼容电缆插入 I2C 连接器

* 将另一端连接到你的 STEMMA QT、Qwiic 或其他 I2C 设备

此外,SPI 引脚头的布局与大多数 8 引脚 I2C 芯片一致,便于使用夹子或插座:

* 将夹子或插座连接到引脚头。注意 1 号引脚,通常插座上会有标记,或排线上的红色/高亮线

* 将夹子连接到目标或将芯片插入插座

最后,JTAG 引脚头也可以用来获取 .1 英寸的独立 I2C 信号:

* 将 8 线 JTAG 线缆连接到 JTAG 连接器

* 将白色 SCL 和灰色 SDA 线缆连接到目标的 I2C 引脚

无论哪种情况,都需要正确设置 Tigard 的开关:

* 在模式选择开关上选择 I2C

* 如果连接在电路中的目标设备有电源,选择 VTGT 选项

* 如果连接的是独立传感器、带电关闭的插座或夹子,请在电压选择器上选择正确电压

#### 特殊情况

FT2232H 的 I2C 实现非常有限。I2C 依赖开漏/开集电极而非推挽三态 I/O,但 FT2232H 支持不佳。因此:

*仅支持控制器模式,不支持设备模式

* 如果 I2C 总线上有其他控制器,Tigard 可能无法正常工作

* 不支持时钟拉伸

* I2C 开关将 DI 和 DO 线短接,以实现双向通信

* 未包含上拉电阻,因为它们通常位于目标板上,而电平转换器上的弱上拉已足够

#### 扩展技巧

为了兼容 I2C 和 SWD,DI 和 DO 通过电阻 R16 合并。这是 SWD 所必需的,通常对 I2C 也可接受。

许多 I2C 目标已有上拉电阻。此外,Tigard 的所有 IO 引脚都有弱 100K 上拉。在测试中,这对大多数 I2C 设备的电路内和外部使用已足够。如果需要更强的上拉,可以临时通过拉高 SPI 引脚的 COPI 和 SCK,或 JTAG 引脚的 TCK 和 TDI 来实现。

#### 软件

libmpsse 是用于控制 MPSSE 或 x232H 系列高速串口的强大库。但由于依赖较多,已不再推荐使用。

pyftdi 是一个新的、简单的接口,与 libmpsse 非常相似:

```

from pyftdi.ftdi import Ftdi

Ftdi.show_devices()

from os import environ

ftdi_url = environ.get('FTDI_DEVICE', 'ftdi://ftdi:2232:1:23f/2')

from i2cflash.serialeeprom import SerialEepromManager

flash = SerialEepromManager.get_flash_device(ftdi_url,'24AA32A',0x50)

flash.write(5,10)

flash.read(0,32)

```

## JTAG 调试(在 JTAG 或 CORTEX 引脚头上)

#### 连接

JTAG 引脚头的布局与 FTDI I/O 引脚标签顺序一致,以与许多 x232H breakout 板保持一致。

此外,CORTEX 引脚头也按标准 ARM 10 针 JTAG 引脚布线。

请务必将模式开关设为 JTAG。这会确保 TDI 和 TDO 分离,并保证 TMS 正确布线到 CORTEX 引脚头。否则,将使用标准连接方式。

#### 软件

**注意:这些 OpenOCD 配置需要 OpenOCD v0.12+**。早期版本可能使用在此提交中更新的已弃用命令:https://github.com/tigard-tools/tigard/commit/5e5722944c8c1ec73b0fa85d574793300c23b3ce

OpenOCD 是用于 ARM、MIPS 等架构的在芯片调试的强大工具。

对应的配置文件(请将其设为链接文件)应如下所示:

```

adapter driver ftdi

transport select jtag

ftdi vid_pid 0x0403 0x6010

ftdi channel 1

adapter speed 2000

ftdi layout_init 0x0038 0x003b

ftdi layout_signal nTRST -data 0x0010

ftdi layout_signal nSRST -data 0x0020

```

在 openocd 中使用:

```

openocd -f tigard-jtag.cfg

```

## JTAG 边界扫描(在 JTAG 或 CORTEX 引脚头上)

边界扫描可用于控制设备以设置 I/O 引脚状态(`EXTEST`),或在设备运行期间查看其状态(`SAMPLE`)。

#### 连接

连接方式与 [JTAG 调试(JTAG 或 CORTEX 引脚头)](#jtag-debug-on-jtag-or-cortex-header) 中所述相同。

引脚布局与运行在 `B` 接口上的 `Olimex ARM-USB-OCD` 兼容。

#### 软件

[UrJTAG](https://urjtag.sourceforge.io/) 是面向底层和边界扫描使用的开源 JTAG 控制软件。

需要告知 UrJTAG Tigard 的 VID 和 PID,以及 JTAG 位于接口 1(默认是 0)。由于一个 bug,TCK 的计算值可能偏高 5 倍——例如下面设置中实际为 500kHz。

[TopJTAG](http://www.topjtag.com/) 是一个更易用但商业($100)且仅限 Windows 的选项。它包含一个“波形视图”,允许你在设备运行时查看任意引脚状态,如同设备上连接了逻辑分析仪。使用 TopJTAG 时,将以下作为 JTAG 连接设置:

* `Connection`:Generic FTDI FT2232

* `Device`:Tigard V1.0 B

* `Static Pins`:Olimex ARM-USB-OCD

* `TCK Freq`:2 MHz(按需调整)

一个支持 Tigard 的开源选项是 [JTAG Boundary Scanner](https://github.com/viveris/jtag-boundary-scanner),它提供 Windows GUI,但后端库是跨平台的(用 C 编写)。该库提供许多功能,例如能够与连接到目标芯片的 SPI 设备通信(警告——速度较慢!)。

该库的 Python 绑定 Alpha 版本可在 [PyJTAGBS](https://github.com/colinoflynn/pyjtagbs) 中获取。例如使用 Tigard 检查扫描链:

```

from jtagbs import JTAGCore, JTAGBS

interface = JTAGCore()

jtag = JTAGBS(interface)

probes = jtag.list_available_probes()

print(probes)

jtag.open_probe('Tigard V1.0 B')

jtag.init_scanchain()

print(jtag.list_devids())

```

有关加载用于切换特定引脚的 BSDL 文件的更多示例,请参见 PyJTAGBS 文档。如果驱动加载正确,应使用的探针名称为 `'Tigard V1.0 A TG100065A'` 和 `'Tigard V1.0 B TG100065B'`。

## SWD(在 CORTEX 引脚头上)

#### 连接

SWD 引脚头是一个标准的 10 针引脚头,常见于许多 SWD 目标开发板。使用两端带有相同引脚头的短“SWD”电缆是连接大多数目标的最佳方式。

请务必将模式开关设为 SWD。这将使用电阻 R16 将 DI 和 DO 连接起来,形成双向 SWDIO 引脚,并连接到 CORTEX 引脚头的 2 号引脚。否则,将使用标准连接方式。

#### 软件

**注意:这些 OpenOCD 配置需要 OpenOCD v0.12+**。早期版本可能使用在此提交中更新的已弃用命令:https://github.com/tigard-tools/tigard/commit/5e5722944c8c1ec73b0fa85d574793300c23b3ce

OpenOCD 是用于 ARM、MIPS 等架构的在芯片调试的强大工具。要在 Tigard 上使用 SWD,需要从源码构建它。AND!XOR DC27 Badge 的 [逐步说明](https://hackaday.io/project/164346-andxor-dc27-badge/log/166464-swd-all-the-things) 涵盖了完整流程。

对应的配置文件(请将其设为链接文件)应如下所示:

```

adapter driver ftdi

transport select swd

ftdi vid_pid 0x0403 0x6010

ftdi channel 1

adapter speed 2000

ftdi layout_init 0x0028 0x002b

ftdi layout_signal SWD_EN -data 0

ftdi layout_signal nSRST -data 0x0020

```

在 openocd 中使用:

```

openocd -f tigard-swd.cfg

```

## iCE40 编程

Lattice iCE40 系列 FPGA 因其低成本和开源工具链而适用于小型项目。虽然这是非常特定的目标,但 Tigard 拥有所有必要的引脚,非常适合编程设备。

#### 连接

所有必要引脚都在 JTAG 引脚头上。

默认未安装“!?”引脚。JTAG 的“!?”引脚与 UART RX 引脚在内部短路,以防你需要刷新 iCE40 但不想焊接 Tigard。详见下表。

请务必在模式选择开关上选择 JTAG/SPI。这会确保 COPI 和 CIPO 分离。

如果计划编程 SRAM 而非 FLASH:

* 交换 COPI 和 CIPO

* 断开 CS 与 FLASH 的连接,但保留其连接到 iCE40

#### 软件

要编程目标的非易失 FLASH,请使用 iceprog:

```

iceprog -I B yourbitstream.bin

```

如果希望直接编程 ice40 的 SRAM,请确保调整布线并再次使用 iceprog:

```

iceprog -I B -S yourbitstream.bin

```

请注意,如果选择编程 SRAM,位流将在断电后丢失。

## AVR ISP

要编程包括许多 Arduino 开发板在内的 AVR 微控制器,请使用带有自定义配置文件的 avrdude。

#### 连接

请务必在模式选择开关上选择 JTAG/SPI。使用 SRST 作为复位信号。

#### 软件

Avrdude 是一个开源的 AVR 烧录工具。Avrdude 7.1 及更高版本已内置对 Tigard 的支持——你只需:

```

avrdude -c tigard

```

对于旧版本,请创建以下 `tigard.conf` 文件,以便将 Tigard 识别为 avrftdi 兼容设备并指定使用的引脚:

```

programmer

parent "avrftdi"

id = "tigard";

desc = "Tigard interface board";

usbdev = "B";

sck = 0;

mosi = 1;

miso = 2;

reset = 5;

;

```

然后,使用 `-C +tigard.conf` 添加配置文件,并使用 `-c tigard` 指定编程器:

```

avrdude -C +tigard.conf -c tigard

```

# 调试

#### PWR 指示灯:

当板子有 USB 供电时该灯会亮起;插入 USB 电缆后应立即点亮。

* 如果不亮,请检查 USB 线缆和电源。

* 如果灯亮后熄灭、变暗或闪烁,很可能线缆或目标存在短路。

#### EN 指示灯:

当 FTDI 芯片正常工作时该灯会亮起,通常在 USB 供电灯亮起后稍亮。

* 如果不亮,可能是 USB 线缆故障、仅供电的 USB 端口/线缆或 FTDI 芯片损坏。

#### VTGT 指示灯:

当电平转换器正常供电时该灯会亮起,无论是由目标供电还是由板载电平选择器供电。

* 如果在 VTGT 模式下不亮,请检查目标供电及与目标的电源和地线连接。

* 如果选择了电压但灯不亮,很可能线缆或目标存在短路。

* 存在某些边界情况,VTGT 可能被[锁存到输出引脚施加的电压](https://github.com/tigard-tools/tigard/issues/20)。养成始终从 VTGT 关闭开始使用的习惯有助于避免此问题。

#### 所有指示灯全亮:

当所有灯都亮起时igard 很可能按预期工作。如果仍有问题,可能性如下(按可能性从高到低排列):

* 是**接线问题**。请确保线缆连接良好,并用万用表确认。

* 是**目标问题**。尝试更换目标以确认软件是否正常工作。

* 是**软件问题**。尝试更换软件工具或模式以确认板子是否正常工作。

* 是**协议问题**。使用逻辑分析仪或示波器观察信号是否正确。

* 是**硬件问题**。尝试更换另一块 Tigard 板。

* 是**Tigard 问题**。尝试更换另一块 x232H 开发板。

# 引脚定义

引脚定义的选择基于易用性原则,具体包括:

* 如果存在广泛使用的标准,优先采用(SWD)

* 如果存在主要的主流用途,采用该方式(SPI/I2C)

* 如果其他常见开发板有对应引脚定义,采用其定义(UART 和 JTAG)

### UART

2.54mm 间距,1x9 针排针。

该引脚定义优先将 FT2232H 引脚按顺序排列——类似于许多 x232H breakout 板。

VTGT、GND、TX、RX 的颜色与大多数 USB-Serial 线缆一致。其余引脚包含但未安装在引脚头上,用户可根据需要选装。

| 引脚编号 | UART 信号 | 颜色 | FT2232H 引脚 |

|----------|-----------|------|--------------|

| 1 | VTGT | 红色 | -- |

| 2 | GDD | 黑色 | -- |

| 3 | TX | 绿色 | AD0 |

| 4 | RX | 白色 | AD1 |

| 5 | RTS | -- | AD2 |

| 6 | CTS | -- | AD3 |

| 7 | DTR | -- | AD4 |

| 8 | DSR | -- | AD5 |

| 9 | DCD | -- | AD6 |

### SWD

1.27mm 间距,2x5 针排针。

这是标准引脚定义。为了兼容 SWD 和 JTAG,模式开关:

1. 将 DI 和 DO 合并为 SWDIO

2. 选择引脚 2 为 SWDIO 或 TMS

| 引脚编号 | SWD 信号 | FT2232H 引脚 | JTAG 信号 | FT2232H 引脚 |

|----------|----------|--------------|-----------|--------------|

| 1 | VTGT | -- | VTGT | -- |

| 2 | SWDIO | BD1 BD2 | TMS | BD3 |

| 3 | GND | -- | GND | -- |

| 4 | SWDCLK | BD0 | TCK | BD0 |

| 5 | GND | -- | GND | -- |

| 6 | NC | -- | TDO | BD2 |

| 7 | KEY | -- | KEY | -- |

| 8 | NC | -- | TDI | BD1 |

| 9 | GND | -- | GND | -- |

| 10 | nSRST | BD5 | nSRST | BD5 |

### JTAG

2.54mm 间距,1x8 针排针。

该引脚定义优先将 FT2232H 引脚按顺序排列——类似于许多 x232H breakout 板。

一般使用时请将模式开关设为 SPI/JTAG 模式。

线缆颜色参考 [SecuringHardware.com](https://SecuringHardware.com/) 使用的 Adafruit FT232H 线缆颜色方案,颜色选择是因为逻辑分析课堂常使用黑、棕、红、橙,因此为线缆选择了这些独特颜色。

该引脚头也可用于 I2C 和 SPI(如果 8 针定义不适用)。

| 引脚编号 | JTAG 引脚 | 颜色 | FT2232H 引脚 |

|----------|-----------|-------|--------------|

| 1 | VTGT | 红色 | -- |

| 2 | GND | 黑色 | -- |

| 3 | TCK | 白色 | BD0 |

| 4 | TDI | 灰色 | BD1 |

| 5 | TDO | 紫色 | BD2 |

| 6 | TMS | 蓝色 | BD3 |

| 7 | TRST | 绿色 | BD4 |

| 8 | SRST | 黄色 | BD5 |

### SPI

2.54mm 间距,2x4 针排针。

该引脚定义专门匹配大多数 8 引脚 SPI 和 I2C 芯片的引脚布局,便于使用夹子或插座连接。

为了兼容 SPI 和 I2C,模式开关:

1. 将 DI 和 DO 合并为 SDA(I2C 模式)

2. 在 I2C 模式下断开引脚 2(用于设备地址信号)

| 芯片引脚编号 | 引脚头编号 | SPI 信号 | FT2232H 引脚 |

|--------------|------------|----------|--------------|

| 1 | 1 | CS | BD3 |

| 2 | 3 | CIPO | BD2 |

| 3 | 5 | WP | 上拉 |

| 4 | 7 | GND | -- |

| 5 | 8 | COPI | BD1 |

| 6 | 6 | SCK | BD0 |

| 7 | 4 | EN | 上拉 |

| 8 | 2 | VTGT | -- |

### LA

1.27mm 间距,2x7 针排针。

LA 端口便于将逻辑分析仪连接到 Tigard 与目标硬件之间的信号,便于监控 UART、SPI 和 JTAG,也通常适用于 I2C。

虽然可以使用 FT2232H 作为简易逻辑分析仪,但这不是设计初衷——预期使用场景是:Tigard 与目标通信,但需借助外部逻辑分析仪调试通信过程。

LA 端口可作为被动机械适配器使用([不支持](https://github.com/tigard-tools/tigard/issues/20))。为获得最佳效果,请给 Tigard 供电但断开 VTGT 与目标的连接,并注意信号完整性。

该端口设计用于直接连接 Bitmagic 逻辑分析仪,或使用 Bitmagic 线缆连接其他工具。

8 个最关键的信号已连接——6 个来自 JTAG/SWD/SPI/I2C 端口,2 个来自 UART 端口。

| 引脚编号 | Bitmagic 信号 | FT2232 引脚 | JTAG 信号 | SPI 信号 | SWD 信号 | I2C 信号 | UART 信号 |

|----------|---------------|-------------|-----------|----------|----------|----------|-----------|

| 1 | xPB0 | BD0 | TCK | SCK | SWCLK | SCL | |

| 2 | xPB1 | BD1 | TDI | COPI | SWDIO | SDA | |

| 3 | xPB2 | BD2 | TDO | CIPO | SWDIO | SDA | |

| 4 | xPB3 | BD3 | TMS | CS | | | |

| 5 | xPB4 | BD4 | TRST | | | | |

| 6 | xPB5 | BD5 | SRST | | | | |

| 7 | xPB6 | AD0 | | | | | TX |

| 8 | xPB7 | AD1 | | | | | RX |

| 9 | GND | | | | | | |

| 10 GND | | | | | | |

| 11 | xTRIG | | | | | | |

| 12 | xCLK | | | | | | |

| 13 | xTRIG2 | | | | | | |

| 14 | xIFCLK | | | | | | |

### I2C

1mm 间距,1x4 针排针,JST SH 兼容。

该引脚定义专门匹配 [Sparkfun 的 Qwiic](https://www.sparkfun.com/qwiic) 和 [Adafruit 的 STEMMA QT](https://learn.adafruit.com/introducing-adafruit-stemma-qt/what-is-stemma-qt) 系统。

使用模式开关选择 I2C/SWD 模式。

| 引脚编号 | I2C 信号 | FT2232H 引脚 |

|----------|----------|--------------|

| 1 | GND | --- |

| 2 | VCC | --- |

| 3 | SDA | BD1 和 BD2 |

| 4 | SCL | BD0 |

### iCE40

使用 JTAG 引脚头,并额外使用未占用的“!?”引脚。

| 引脚编号 | 标签 | iCE40 信号 | FT2232 引脚 |

|----------|-------------|--------------|--------------|

| 1 | VTGT | VTGT | --- |

| 2 | GND | GND | --- |

| 3 | TCK | CLK | BD0 |

| 4 | TDI/MOSI/SDA| MOSI/COPI | BD1 |

| 5 | TDO/MISO/-- | MISO/CIPO | BD2 |

| 6 | TMS/SS/-- | --- | --- |

| 7 | TRST/CS/ICE_SS_B | CS/ICE_SS_B | BD4 |

| 8 | SRST/CRESET | RESET | BD5 |

| 9 | !? | CDONE | BD6 |

JTAG 的“!?”引脚与 UART RX 引脚内部短路,以便在不焊接 Tigard 的情况下刷新 iCE40。

### AVR ISP

常见于 AVR 开发板的 6 针 ICSP 引脚头需要以下连接:

| 引脚编号 | 标签 | ISP 信号 | ICSP 引脚 | FT2232 引脚 |

|----------|-------------|----------|-----------|--------------|

| 1 | VTGT | VTGT | 2 | --- |

| 2 | GND | GND | 6 | --- |

| 3 | TCK | SCK | 3 | BD0 |

| 4 | TDI/MOSI/SDA| MOSI | 4 | BD1 |

| 5 | TDO/MISO/-- | MISO | 1 | BD2 |

| 6 | TMS/SS/-- | --- | --- | --- |

| 7 | TRST/-- | --- | --- | --- |

| 8 | SRST/RST | RST | 5 | BD5 |

# 条纹与尾巴

为了支持不同接口,可以使用定制布线或扩展板。推荐名称:“Tigard Stripes”指扩展板,“Tigard Tails”指布线。

* `UART Tail` 随板附带,包含 VTGT、GND、TX 和 RX

* `JTAG Tail` 随板附带,包含标好的多用途 JTAG、SPI 和 I2C 信号线

* `SOIC8 Tail` 指带排缆的廉价 SOIC-8 夹具,兼容 SPI/I2C 引脚头

# Dens(外壳)

Tigard 以裸板形式提供,但有多种 3D 打印的安装座和外壳(“Dens”)可供选择:

* 第一个 [TigarDen](https://github.com/hamid-elaosta/TigarDen) 由 hamid 设计,是用于固定 Tigard 的多件式上下外壳

* [底部外壳](https://www.thingiverse.com/thing:5166570) 由 phaktor 设计,底部有漂亮的虎纹,或可单色打印

* [带铰链的外壳](https://www.thingiverse.com/thing:5169952) 由 professor_plum 设计,可容纳 Tigard、Bitmagic 和多个探针

* [简化 2 件式外壳](https://cad.onshape.com/documents/832906f0b96360664fedfe62/w/f1b917fd93e5b559c0927cf4/e/eb5666e6e328afd821567f83) 由 jwise 设计,适用于铣削或打印

* [tigard-tray](https://github.com/tigard-tools/tigard-tray) 是一个 3D 打印托盘,可固定 Tigard、Bitmagic 和 9 个探针夹,同时保护引脚,便于在拉链包中滑动

# 序列号

Tigard 遵循序列号分配约定。如果你决定自行制作并销售 Tigard,请将前两个字符 “TG” 替换为其他内容。

格式:`TGMmxxxx`

* `TG` — 固定标识,表示 “Tigard”

* `M` — 主版本号(十进制)

* `m` — 次版本号(十进制)

* `xxxx` — 4 位小写十六进制序列号,从 0 开始补零

## 已分配

* 第一批 28 个(2020 年 7 月 5 日):TG010000 - TG01001b

* 第二批 42 个(2020 年 8 月 5 日):TG01001c - TG010046

* 第三批 496 个(2020 年 10 月):TG100000 - TG1001f0

* 第四批 693 个(2021 年 1 月):TG110000 - TG1102b5

* 第四批 697 个(2021 年 9 月):TG110400 - TG1106b9注意:该批次的通孔元件未使用选择性焊锡机焊接,部分需要返工,因为“hack”跳线被焊锡意外桥接。 * 第五批 1400 个(2022 年 11 月):约 TG110700 - TG110c7f * 第六批 1400 个(2024 年 1 月):约 TG110c80 - TG 1111ff

注意:该批次 JTAG 引脚头安装位置错误。应该是 8 针引脚头安装在 9 孔的插座中。插座第 9 脚应为空(仅用于刷写 ice40 FPGA 的 icebreaker)。但第 1 脚被错误地留空。我添加了 1 脚的头并修剪了第 9 脚,以便 8 针 JTAG 线缆无法插错,同时 9 针 UART 插座不会误用。 * 第七批 2100 个(2025 年 1 月):约 TG111200-TG111834 # 获取 Tigard ## 在哪里购买 Tigard 可直接从以下渠道购买: * [Crowd Supply](https://www.crowdsupply.com/securinghw/tigard) * [Mouser](https://www.mouser.com/ProductDetail/Securing-Hardware/TIGARD-V1?qs=aP1CjGhiNiFnjSEE%2FnXyEw%3D%3D) * [1BitSquared](https://1bitsquared.com/collections/embedded-hardware/products/tigard) [HackerWarehouse](https://hackerwarehouse.com/product/tigard/) 也提供由 SynapticRewrite 设计的 [激光切割亚克力外壳](https://hackerwarehouse.com/product/tigard-case/)。 Tigard 在欧洲可通过 [1BitSquared 的德国商店](https://1bitsquared.de/products/tigard) 购买。 10 块以上可享受折扣,直接从 [SecuringHardware.com](https://learn.securinghardware.com/product/tigard/) 批量订购。联系 tigards - at - securinghw.com 获取批发订单。 ## 自行制作 Tigard Tigard 采用 [CC-BY-SA 4.0 许可证](https://github.com/tigard-tools/tigard/blob/master/LICENSE.txt) 发布。这意味着你被允许并鼓励自行制作设备,或在 Tigard 设计基础上进行修改,只要注明项目来源并共享你的修改。 如果你选择自行制造ard 电路板,我们建议/要求: * 以某种方式区分你的电路板——选择不同颜色可能是最简单的方式,以免与 SecuringHardware.com 的电路板混淆 * 你可以称其为 “Tigard” 并将其写入 EEPROM 的 USB 产品描述符 * 在 EEPROM 中写入准确的制造商信息 * 使用不与上述[已列出的序列号](#serial-numbers)冲突的序列号——不要使用 “TG” 前缀 SecuringHardware.com 测试、验证并支持其生产和销售的每一块 Tigard。如在制作设备时发现[设计问题](https://github.com/tigard-tools/tigard/issues),请告知我们;但如果你购买的是第三方 Tigard 并遇到硬件问题,你需要与卖家或制造商联系解决。

标签:avrdude, AVR ISP, Flashrom, FTDI FT2232H, I2C, iCE40, iceprog, JTAG, libmpsse, OpenOCD, pyftdi, SPI, SWD, Tigard, UART, URJTAG, USB-Serial, USB转串口, 多协议, 开源硬件, 硬件 hacking, 硬件探测, 硬件接口, 硬件黑客, 逆向工具