hello-akhilesh/FPGA-Based-Real-Time-Fall-Detection-System-using-Verilog

GitHub: hello-akhilesh/FPGA-Based-Real-Time-Fall-Detection-System-using-Verilog

基于FPGA的实时跌倒检测系统,通过Verilog硬件实现低延迟的边缘检测与告警。

Stars: 0 | Forks: 0

# 🧠 基于FPGA的实时跌倒检测系统

## 📌 概述

本项目实现了一个**基于FPGA的实时跌倒检测系统**,采用轻量级、硬件高效的方法。

该系统使用**信号处理与规则逻辑**,而非复杂的机器学习模型,从而在FPGA硬件上实现**低延迟、可靠的推理**。

## 🚀 关键特性

* ⚡ 实时跌倒检测(无需云端)

* 🔁 单脉冲检测

* 🚨 告警锁存(持续紧急信号)

* 🧩 完全模块化的Verilog设计

* 📉 低资源占用

## 🧠 检测逻辑

系统通过以下方式检测跌倒:

* 加速度的突然峰值

* 随后进入静止状态

### 规则:

```

IF (spike_count ≥ 1)

AND (mean < threshold for 3 cycles)

AND (not previously detected)

→ FALL DETECTED

```

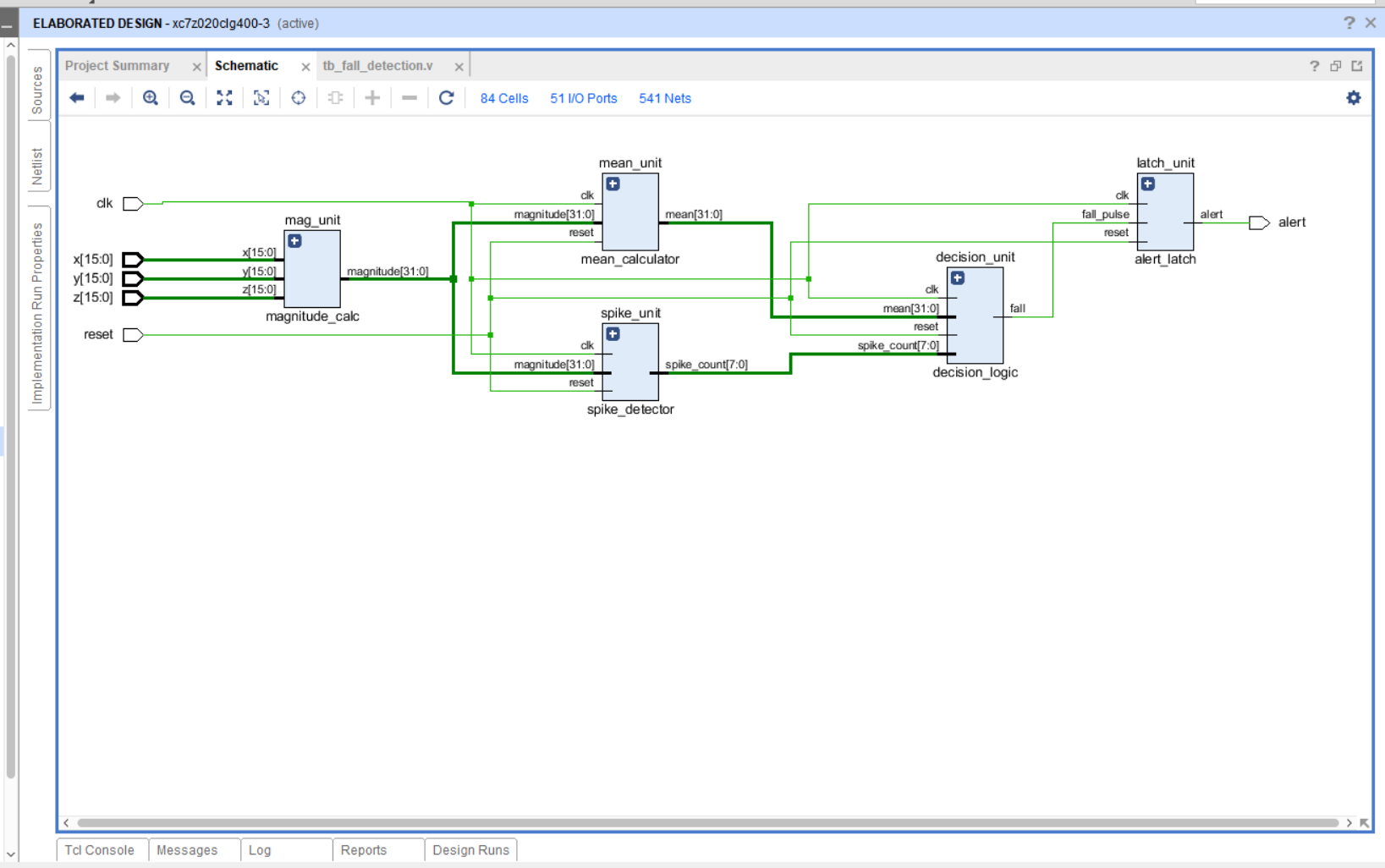

## 🏗️ 系统架构

基于流水线硬件设计:

```

Accelerometer (x, y, z)

↓

Magnitude Calculation

↓

Spike Detection

↓

Mean Calculation

↓

Decision Logic

↓

Alert Latch → ALERT

```

## 🧩 RTL模块

- `magnitude_calc.v` → 计算 √(x² + y² + z²)

- `spike_detector.v` → 检测加速度的突然峰值

- `mean_calc.v` → 计算运行均值以检测静止

- `decision_logic.v` → 应用跌倒检测条件,并使用 `fall_prev` 实现单脉冲逻辑

- `alert_latch.v` → 在系统复位前保持告警信号

- `top_module.v` → 集成所有模块构成完整流水线

## ⚙️ 工具与硬件

* **Vivado Design Suite(RTL流程)**

* **Verilog HDL**

* **目标FPGA:** ZedBoard

* **时钟频率:** 50 MHz

## 📊 性能

* ⏱️ 极低延迟(几个时钟周期)

* ⚡ 实时处理

* 🔋 低功耗

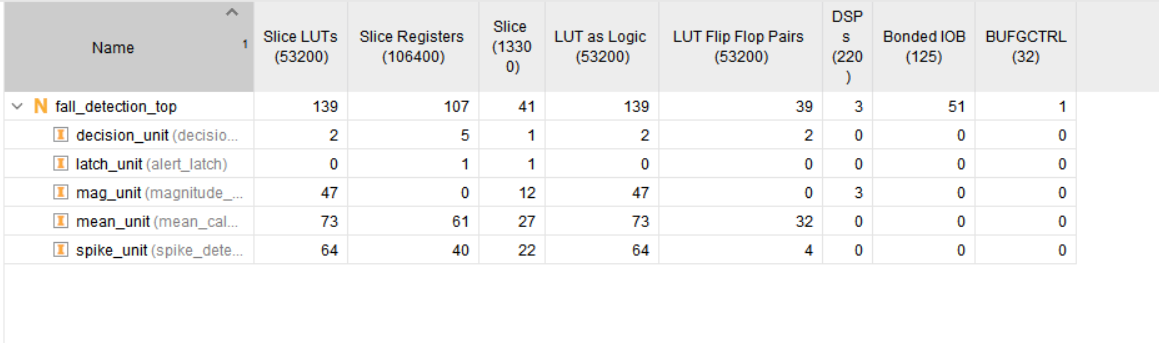

* 📉 LUT/FF使用量极少

## 📁 项目结构

```

├── src/ # Verilog source files

├── sim/ # Testbench files

├── constraints/ # XDC file

├── results/ # Simulation screenshots

├── README.md

```

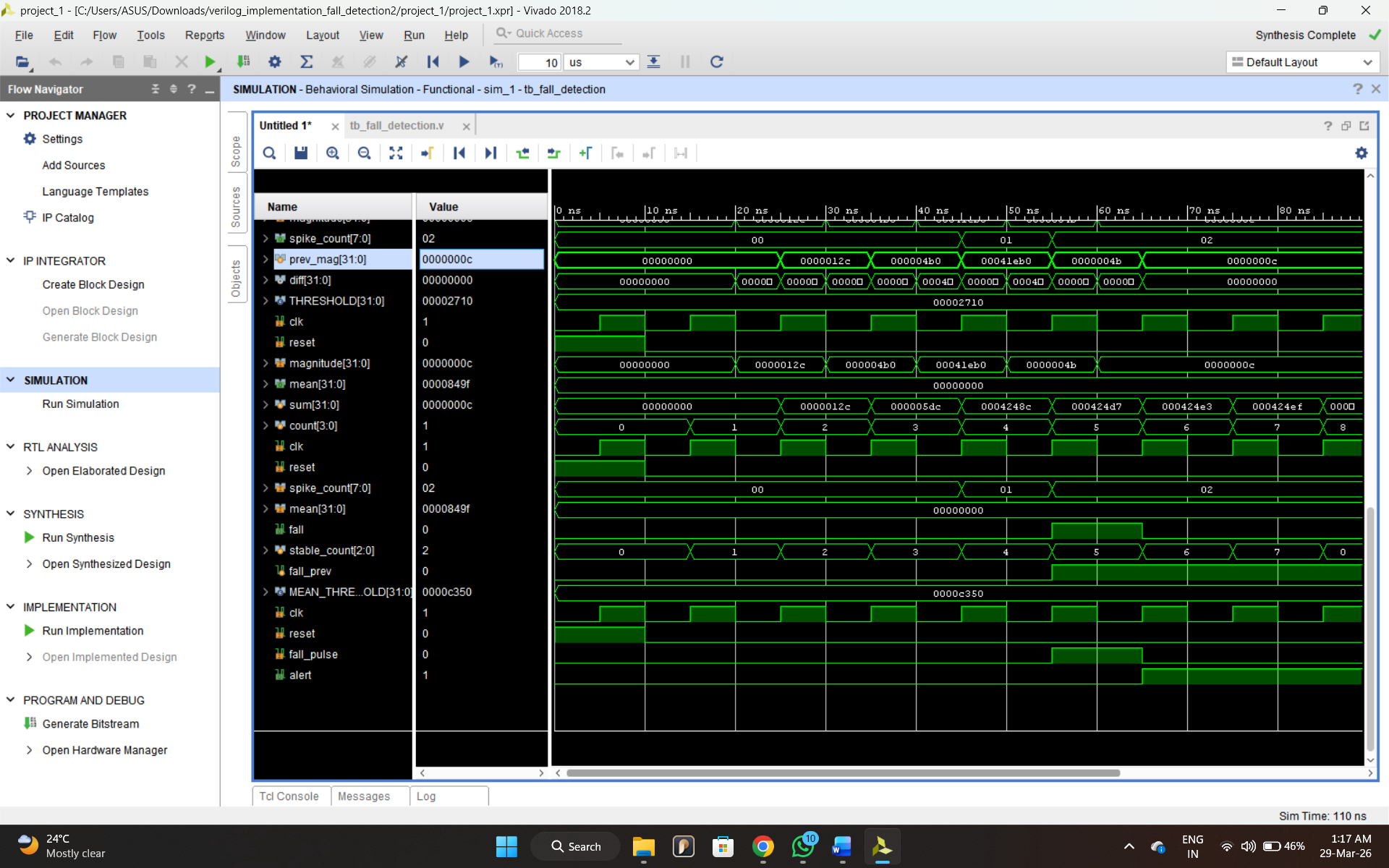

## 📊 结果

### 波形图

### RTL原理图

### 资源利用率

## 📌 应用场景

* 老年人监护系统

* 可穿戴医疗设备

* 实时安全系统

标签:50MHz, FPGA, Verilog, Vivado, ZedBoard, 云计算, 低延迟, 低资源占用, 信号处理, 决策逻辑, 实时跌倒检测, 峰值检测, 嵌入式系统, 时序电路, 硬件加速, 硬件实现, 紧急告警, 规则引擎, 边缘AI, 运行均值, 门级设计