pigasus-hls/RapidDetect-RCC

GitHub: pigasus-hls/RapidDetect-RCC

基于 HLS 的 200Gbps 异构 FPGA-CPU 硬件加速威胁检测系统,使用 Sigma 规则对流式日志进行低延迟高吞吐检测。

Stars: 0 | Forks: 0

# RapidDetect on V80

RapidDetect 是一个基于 HLS 的 200Gbps (@400MHz) 硬件加速威胁检测系统,用于对使用 [Sigma](https://github.com/sigmahq/sigma) 规则的流式结构化系统日志进行检测。该仓库是为 FCCM 2026 可重构计算挑战赛准备的,包含了完整的 RapidDetect FPGA 流水线的 Vitis HLS 实现。

灵感来源于 [Pigasus 入侵防护/检测系统](https://www.usenix.org/conference/osdi20/presentation/zhao-zhipeng),RapidDetect 采用异构的 FPGA 和 CPU 架构,以实现高吞吐量和低延迟的流式系统日志威胁检测。此版本针对 V80(占用不到 1/3 的 SLR)构建,使用 AVED 作为起点,并通过 QDMA 在主机与 FPGA 之间传输数据和控制信息。多字符串模式匹配器(MSPM)能够以 200Gbps 的速率处理超过 10,000 个字符串字面量(目前基于约 200 条 Linux Sigma 规则可达 >4000 个字面量)。随后,连接模式匹配器(CPM)会检查通过 MSPM 的日志,仅针对在 MSPM 中匹配成功的规则进行验证。使用类似布隆过滤器的指纹,CPM 可以检查字符串字面量的逻辑与(AND)组合,从而显著降低误报率。

从高层次来看,下图展示了本仓库中实现的系统。HBM 被用作未来支持通过以太网直接从网络进行流式输入的替代方案,FPGA 作为网络链路中的内联设备。

更多关于应用程序和系统的详细信息可以在 [系统描述](./SYSTEM.md) 中找到。

RapidDetect 是卡内基梅隆大学的 [Shashank Obla](https://github.com/shashankov) 和 [James C. Hoe](https://users.ece.cmu.edu/~jhoe/doku/doku.php) 与弗吉尼亚大学的 [Tommy Tracy II](https://github.com/tjt7a)、Wajih Ul Hassan 和 Kevin Skadron 之间的持续合作项目。

## 需求

### 系统要求(来自 AVED)

- RHEL 9.4(内核 5.14)或 Ubuntu 24.04(内核 6.8)

### 软件先决条件

- Python 3.6.8 或更高版本(用于 AVED)

- Cmake 3.5.0 或更高版本(用于 AVED)

- Vivado 和 Vitis 2025.1

- [Alveo Versal Example Design (AVED)](https://xilinx.github.io/AVED/latest/How-to%2Binstall%2Band%2Brun%2Ba%2Bpre-built%2BAVED%2Bdesign%2Bon%2Ban%2BALVEO%2Bcard.html)。请务必[在 V80 上刷入预构建的设计](https://xilinx.github.io/AVED/latest/AVED+Updating+FPT+Image+in+Flash.html),并按照链接中的说明安装主机侧 AMI 工具。

- [QDMA Linux 驱动](https://github.com/Xilinx/dma_ip_drivers/tree/master/QDMA/linux-kernel) 已[在此仓库中作为子模块包含](./dma_ip_drivers),需要按照 [AVED 的说明](https://xilinx.github.io/AVED/latest/AVED%2BQDMA.html) 和 [QDMA 文档](https://xilinx.github.io/dma_ip_drivers/master/QDMA/linux-kernel/html/build.html) 进行构建和安装。请务必使用 `sudo make install` 同时安装内核驱动和相关应用程序。

### AVED 的 IP

从 [Alveo V80 加速器卡早期访问网站](https://www.xilinx.com/member/v80.html) 下载 SMBus IP。将 IP 复制到 AVED 硬件设计中,如下目录树中的星号(*)所示。在构建设计之前必须完成此步骤。

```

hardware

└── AVED

└── hw

└── amd_v80_gen5x8_25.1

└── src

└── iprepo

├── cmd_queue_v2_0

├── hw_discovery_v1_0

├── shell_utils_uuid_rom_v2_0

└── smbus_v1_1*

```

### 假设分析集成

可选地,你可以选择运行带有假设分析(Hyperscan)集成的完整系统,将输出数据从 FPGA 传输到主机上运行的假设分析引擎。这将需要一些额外的先决条件,如下所述:

- 假设分析(Hyperscan):假设分析仓库已作为子模块包含在此仓库中,必须根据其 [说明](https://intel.github.io/hyperscan/dev-reference/getting_started.html) 进行构建。其部分额外的子依赖项包括(并在 Ubuntu 上安装的说明):

- Ragel(`sudo apt install ragel`)

- Boost(`sudo apt install libboost-dev`)

使用 `./software/hyperscan/build` 作为构建目录以遵循标准构建流程。如果使用不同的构建目录,需要编辑 Makefile 指向该目录(后续有说明)。

- Boost 头文件:假设分析还需要 Boost 用于 FPGA 主机代码与假设分析引擎之间的共享内存通信。只要在适当的 Makefile 中指定 Boost 路径,本地安装也是可行的。

- Boost(`sudo apt install libboost-dev`)

- Boost 线程(`sudo apt install libboost-thread-dev`)

## 如何运行 RapidDetect

在环境中设置所需版本的 Vitis,通过执行 Vitis 安装目录中的 `source settings64.(c)sh` 脚本。

### 运行 C 仿真

通过导航到 [`hardware`](./hardware) 目录并执行测试台 Python 脚本来运行 C 仿真测试台。

```

cd hardware

vitis -s scripts/rapidd_testbench.py

```

这将创建一个包含 Vitis 工作区和测试台的 `hls_workspace` 文件夹。脚本的输出应如下所示:

```

****** Vitis Development Environment

****** Vitis v2025.1 (64-bit)

**** SW Build 6137779 on 2025-05-21-18:10:04

** Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

** Copyright 2022-2025 Advanced Micro Devices, Inc. All Rights Reserved.

Vitis Server started on port 'XXXXX'.

Running CSim for MSPM only. This can take a few minutes...

C Simulation log can be found at ./hls_workspace/smonly/smonly/logs/hls_run_csim.log

C Simulation output matches the golden output. Test PASSED.

Running CSim for full RapidDetect. This can take a few minutes...

C Simulation log can be found at ./hls_workspace/rapidd/rapidd/logs/hls_run_csim.log

C Simulation output matches the golden output. Test PASSED.

```

### 构建 HLS 内核

与 C 仿真类似,所有 HLS 内核都可以使用 Python [脚本](./hardware/scripts/rapidd_synthesis.py) 构建,如下所示:

```

cd hardware

vitis -s scripts/rapidd_synthesis.py

```

这将在 `hls_workspace` 文件夹中创建所有内核作为 Vitis 工作区中的组件。这可能需要一些时间。可以通过直接修改 Python [脚本](./hardware/scripts/rapidd_synthesis.py) 来调整内核的参数化。

你可以通过在 Vitis 中打开工作区来查看该工作区:

```

vitis -w ./hls_workspace

```

### 构建带有 RapidDetect 的 AVED 设计

以下说明与 [AVED 文档](https://xilinx.github.io/AVED/latest/How-to%2BRebuild%2Ban%2BAVED%2BDesign%2Bfor%2BYourself.html) 中的步骤非常接近。已修改脚本以指向 HLS 工作区、创建包含连接到 AVED 的 RapidDetect IP 的块设计,并对构建流程进行适当调整以实现时序收敛。

导航到 hardware 目录并运行 build_all.sh 脚本来构建 RapidDetect 硬件。

```

cd hardware/AVED/hw/amd_v80_gen5x8_25.1

./build_all.sh

```

构建目录将包含 Vivado 项目。你可以使用以下命令打开此项目(探索该构建的 Vivado 块设计):

```

cd hardware/AVED/hw/amd_v80_gen5x8_25.1

vivado build/prj.xpr &

```

在 Vivado IDE 启动并加载指定项目后,在 Flow Navigator 窗格中找到 IP INTEGRATOR,然后点击“Open Block Design”。

### 编程设计

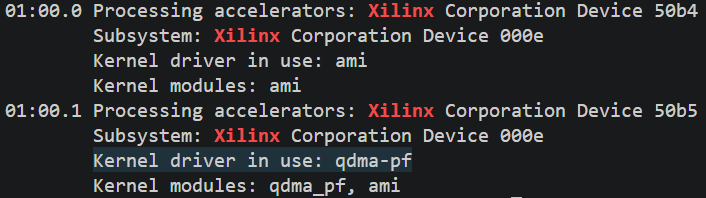

你将使用 AMI 的 cfgmem_program 命令,指定卡的 BDF、设计 PDI 的路径以及要编程的闪存分区。在此示例中,BDF 为 01:00.0(你可以使用以下命令查找设备的 BDF:`lspci -k | grep -i xilinx -A 2`)

```

cd hardware/AVED/hw/amd_v80_gen5x8_25.1

sudo ami_tool cfgmem_program -d 01:00.0 -t primary -i ./build/amd_v80_gen5x8_25.1_nofpt.pdi -p 0

```

成功编程的提示信息为“OK. Image has been programmed successfully.”。随后会自动执行热复位以在分区 0 中启动更新后的设计。你可以使用 AMI 工具重置 PCIe 和驱动,并使用以下命令检查 `qdma-pf` 驱动是否已加载到 QDMA 物理功能:

```

sudo ami_tool reload -d 01:00.1 -t driver

lspci -k | grep -i xilinx -A 2

```

你应该看到如下输出(你的 BDF 可能与图中所示的 01:00.0/1 不同):

### 构建和编译主机代码

设置 QDMA 队列使用 setup_queues.sh 脚本。

```

cd software

sudo ./setup_queues.sh

```

#### 无假设分析运行

使用 make 构建主机代码并运行它。这将在 FPGA 上运行内置测试。

```

make host.x

sudo ./host.x

```

要运行真实跟踪(提供的跟踪文件源自 [DARPA 透明计算计划](https://www.darpa.mil/research/programs/transparent-computing),在 [Engagement #5](https://github.com/darpa-i2o/transparent-computing) 期间生成),请先解压 [traces 目录](./traces) 中的跟踪文件,然后按如下方式执行主机代码:

```

make -C ../traces

sudo ./host.x ../traces/E5_cadets-deduplicated.json.500k

```

预期性能约为 172Gbps(其中包括将日志事件按换行符拆分的打包开销)。

#### 带有假设分析的运行

确保已安装先决条件和假设分析(包括 Boost)。编辑 [Makefile](./software/Makefile) 以指向你的假设分析和 Boost 安装路径(如果与标准路径不同);Makefile 会在 hyperscan/build 中查找假设分析,并在系统范围内安装时查找 Boost。

构建主机代码以及假设分析消费者代码:

```

make host_producer.x

make hyperscan_consumer.x

```

打开两个终端,一个用于运行生产者,另一个用于运行消费者。使用 FPGA 编程好比特流后(使用上述说明),运行以下命令。请根据你的机器使用适当数量的线程,并确保两个命令之间。

```

# 终端 1(首先运行)

sudo ./host_producer ../traces/E5_cadets-deduplicated.json.500k

# 终端 2(查找由生产者创建的共享内存区域)

sudo ./hyperscan_consumer patterns_full.db

```

你应该会看到一个新文件 [all_detections.log](./software/all_detections.log),其中包含通过 FPGA 和假设分析并被 RapidDetect 标记为恶意的所有事件的子集。此实现的性能需要针对新机器进行调优,如果没有足够的内核(对于此给定跟踪,你可能需要超过 24 个内核才能让假设分析处理来自 FPGA 的速率),你可能无法看到完整带宽。

标签:200Gbps, AMSI绕过, AVED, Bloom Filter, CPM, CPU, FCCM, FPGA, HBM, HLS, James C. Hoe, MSPM, QDMA, Reconfigurable Computing Challenge, Shashank Obla, Sigma规则, UML, V80, Versal, Vitis HLS, 以太网, 低延迟, 合取模式匹配, 多字符串模式匹配, 威胁检测, 客户端加密, 异构计算, 流处理, 目标导入, 硬件加速, 系统日志, 逆向工具, 重配置计算, 高吞吐, 高速日志监控