Adhiraj4/Sobel-Edge-detection-and-inference-based-Image-Compositing-using-Vitis-HLS-for-Pynq-Z2-FPGA

GitHub: Adhiraj4/Sobel-Edge-detection-and-inference-based-Image-Compositing-using-Vitis-HLS-for-Pynq-Z2-FPGA

基于 Vitis HLS 在 PYNQ-Z2 FPGA 上实现 Sobel 边缘检测与边缘密度驱动的实时图像合成。

Stars: 0 | Forks: 0

# 使用 Vitis-HLS 为 Pynq-Z2 FPGA 实现基于 Sobel 边缘检测与推理的图像合成

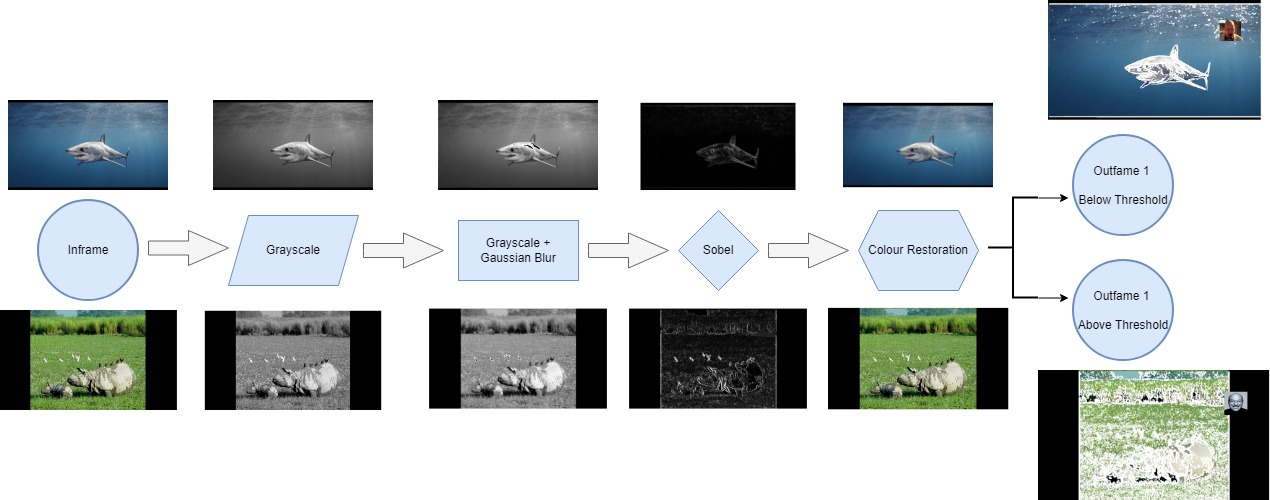

Sobel 边缘检测用于图像边缘检测。基于整个帧的边缘密度,在帧的右上角合成一幅 128 x 128 的小图像。输入像素首先被转换为灰度,然后使用标准差 ($\sigma$) 为 3 的 7x7 高斯模糊核对灰度图像进行模糊处理。

7x7 窗口在水平和垂直方向上滑动。为此创建了行缓冲,为了使设计算法高效,采用了循环缓冲,而不是在内存中进行逐行移位。

利用循环行缓冲的相同原理,使用 3x3 滑动窗口获取 Sobel 边缘检测的 x 和 y 梯度。此外,初始彩色像素值通过流水线存储,并根据边缘密度决定显示彩色像素还是全白像素,从而在彩色图像上呈现出非传统的边缘视觉效果。

最后,在一整帧通过后,计算像素图像的总边缘密度,并根据低/高密度在右上角合成不同的图像。

为了将图像转换为像素数据,提供了一个 Python (.py) 程序;用户可以根据需要使用它来获取自己的自定义图像。

应用包括检测脑肿瘤、车道监控等。

图像数据位于 compositing.hpp 文件中。

该项目是为 Xilinx PYNQ-Z2 板卡完成的,所选部件为 \textbf{xc7z020clg400-1}。design.bd 文件是 [AXI Video DMA (AXI VDMA)](https://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html/)。在视频流中,Sobel IP 必须放置在 hdmi\_in 和 axi\_vdma 模块之间。必须添加一个额外的 AXI 主引脚,并将其连接到 VDMA 视频流 IP 内部的 Interconnect IP。该 IP 必须连接到 142 MHz 时钟以及设计中存在的相应复位信号。端口类型使用了 s_axilite。

为了方便用户,提供了已综合的 base.bit(比特流)和 base.hwh(硬件交付)文件,以及用于在 Xilinx Pynq 提供的 [Jupyter 生产力平台](https://pynq.readthedocs.io/en/v2.6.1/getting_started.html)上运行视频的 .ipynb 文件。

标签:AXI VDMA, FPGA开发, NoSQL, PYNQ-Z2, Sobel算子, UML, Verilog/VHDL, Vitis HLS, Xilinx, Zynq, 图像合成, 图像处理, 嵌入式系统, 灰度转换, 硬件加速, 脑肿瘤检测, 行缓存, 视频流处理, 计算机视觉, 车道监测, 边缘检测, 逆向工具, 逻辑综合, 高斯模糊