davidorlian/DES-verilog

GitHub: davidorlian/DES-verilog

在 Verilog 中实现 DES 硬件电路并完成 FPGA 落地,提供从 RTL 到时序闭合的完整设计验证流程。

Stars: 0 | Forks: 0

# DES 在 Verilog 中的实现

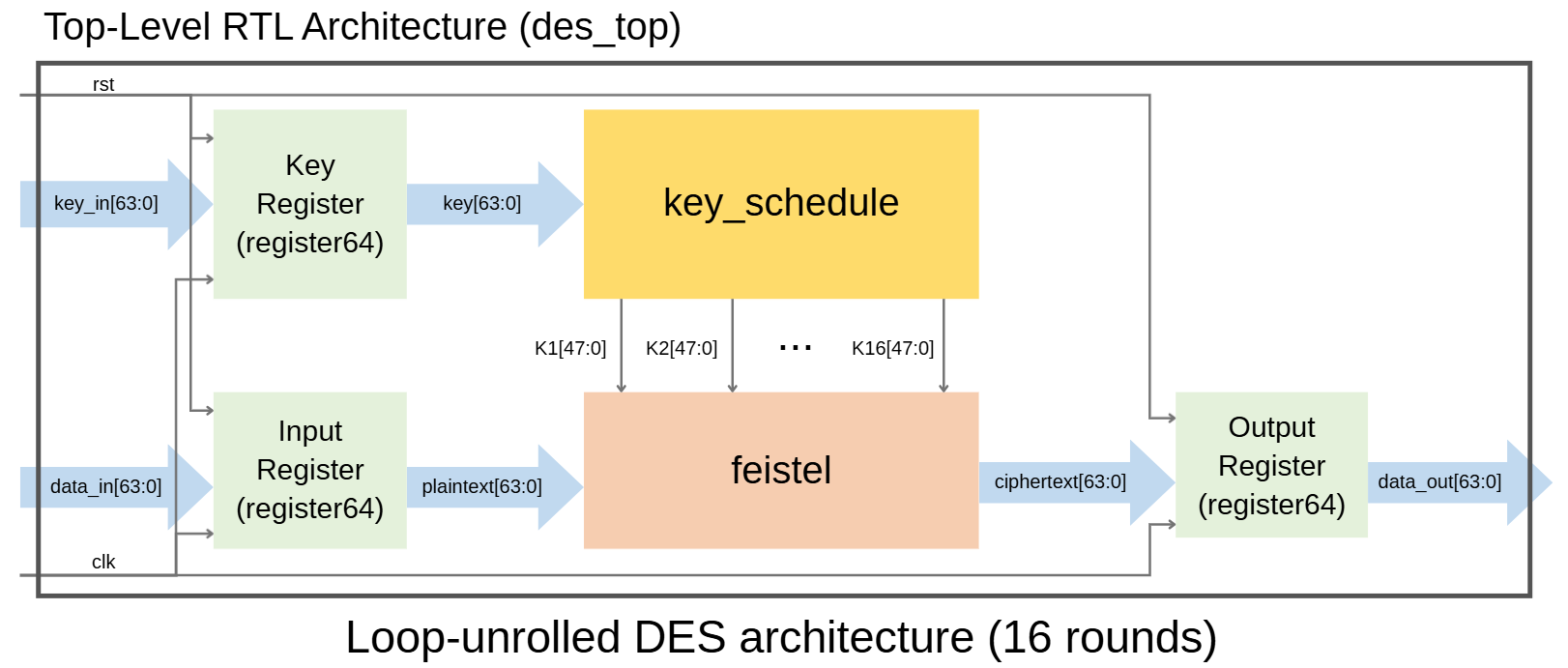

在 Verilog 中实现数据加密标准(DES)的硬件实现,涵盖从 RTL 到综合、布局布线以及后布线时序仿真的完整数字设计流程。该设计实现了一个 16 轮循环展开的 Feistel 架构,并对密钥调度、置换以及 S 盒替换逻辑进行了完整模块化分解。使用基于 Python 的测试向量生成流程驱动自检查测试平台,验证已知 DES 参考向量。综合后在 Artix-7 FPGA 上达到约 55 MHz 频率,消耗约 1455 个 LUT。

## 本项目展示内容

- 非平凡加密算法的 RTL 实现

- 模块化硬件分解:密钥调度、置换、S 盒替换

- 基于外部生成测试向量的参考驱动验证方法

- 完整设计流程:RTL → 仿真 → 综合 → 布局布线 → 后布线时序验证

- 基于 Python 的自动化验证数据准备

- 使用位级分析进行系统性调试

## 架构概述

### 系统级设计

[](docs/architecture/des_encryption_block_diagram.png)

顶层模块 `des_top` 集成以下部分:

- `key_schedule` — 生成 16 轮子密钥

- `feistel` — 执行 16 轮 Feistel 网络

- 输入、密钥与输出的内部寄存器

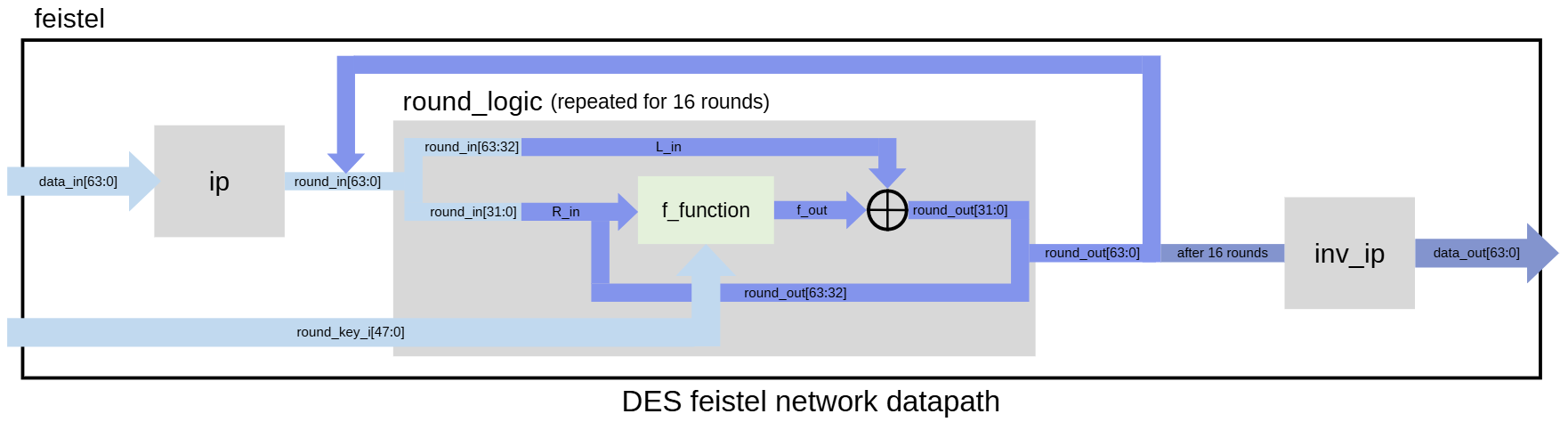

### Feistel 网络

[](docs/architecture/des_feistel_network.png)

RTL 模块直接映射到 DES Feistel 结构:

- `ip` — 初始置换

- `round_logic` — 轮级变换

- `f_function` — 核心非线性轮函数

- `inv_ip` — 最终置换

该设计实现为一个循环展开的组合数据通路:显式实例化全部 16 个 Feistel 轮,仅在输入与输出边界保留寄存器。

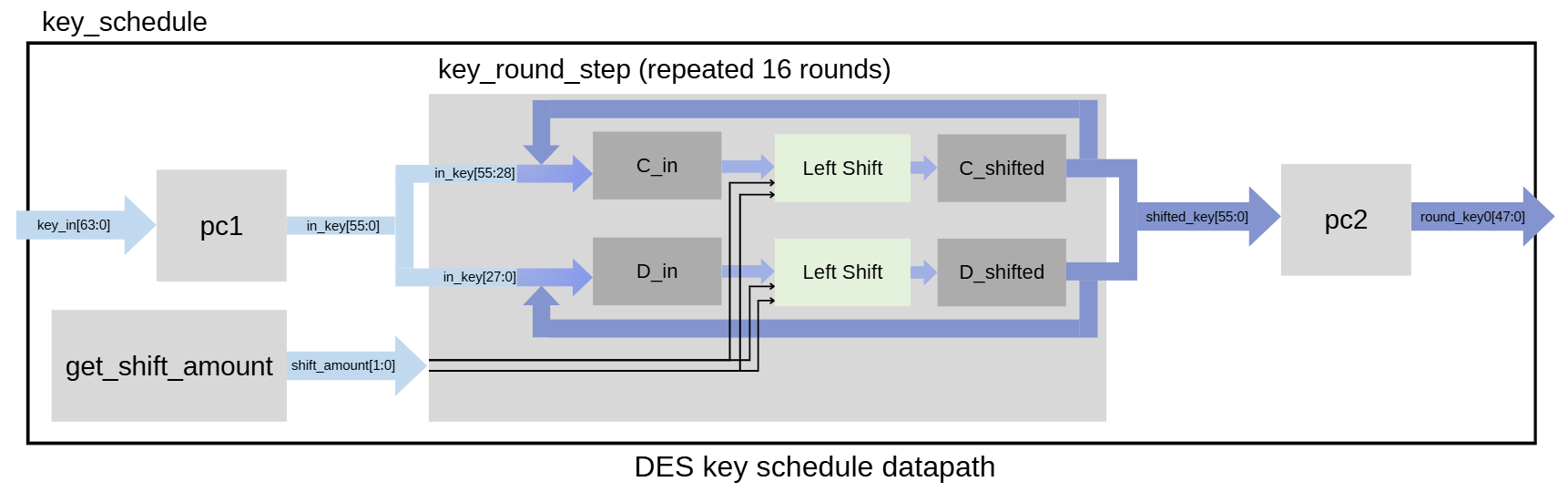

### 密钥调度

[](docs/architecture/des_key_schedule.png)

密钥调度被分解为:

- `pc1` — 初始密钥置换

- `key_round_step` — 每轮移位逻辑

- `pc2` — 子密钥提取

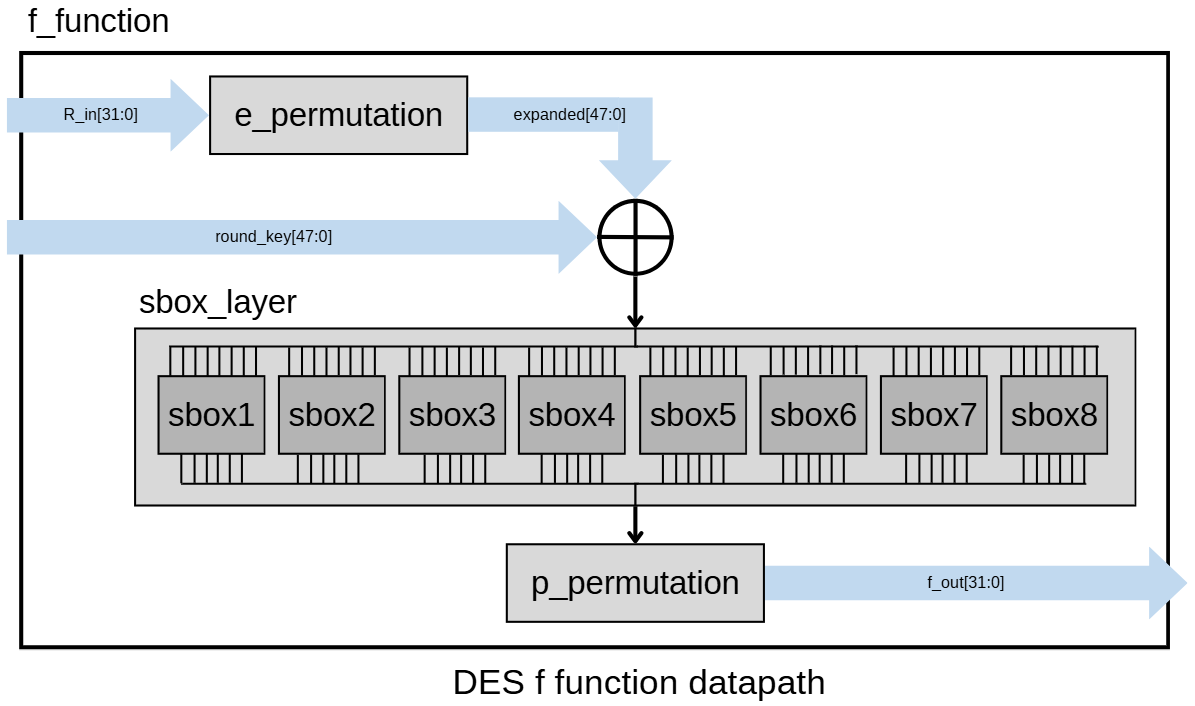

### F 函数

[](docs/architecture/des_f_function.png)

轮函数流水线:

- `e_permutation` — 从 32 位扩展到 48 位

- `sbox_layer` — 通过 8 个 S 盒(`sbox1`–`sbox8`)实现非线性替换

- `p_permutation` — 最终置换阶段

## 验证

设计使用自检查测试平台驱动的外部参考向量进行验证。

验证流程包括:

- 已知 DES 参考向量

- 使用解析中间 DES 状态的模块级验证

- 与 PASS/FAIL 报告自动比对输出

### 测试向量生成

一个基于 Python 的工作流生成并验证 DES 测试向量,使用可信的外部 DES 参考(JS-DES)。提取中间轮值,归一化并转换为 Verilog 兼容的测试平台输入,从而实现模块级与系统级覆盖,且不依赖手动编写的测试数据。

更多细节请参见 [测试向量文档](docs/test_vectors/README.md)。

### 调试示例

在验证过程中,观察到仿真输出存在系统性的位级不匹配。将十六进制转换为二进制后,发现一致的取反模式(0 → 1,1 → 0),这立即将搜索范围缩小到置换阶段而非功能逻辑。根本原因在于某个置换块中的位序错误。修正后,所有不匹配得以解决。

这是一个良好示例,说明识别系统性错误模式(而非调试完整数据通路)如何显著减少调试时间。

## 结果

- 功能仿真:**通过**(RTL 与后 P&R 一致)

- 加密输出与已知 DES 参考向量匹配

关键路径遍历全部 16 轮,这解释了约 55 MHz 的 Fmax。

### FPGA 实现(Artix-7)

| 指标 | 值 |

|---|---|

| Fmax(后综合) | ~55 MHz |

| LUT | ~1455 |

| 触发器 | ~184 |

详细报告请参见 [docs/reports](docs/reports/)。

## 仿真

使用 ModelSim 执行仿真。运行完整流程:

```

vsim -do sim/run.do

```

这将编译所有 RTL 与测试bench文件,加载波形并运行仿真至完成。

## 替代集成封装

`des_top_wrapper` 是一个可选模块,用于降低 I/O 要求的集成场景。它通过选择器接口以 32 位共享总线加载 64 位密钥与输入块,并提供 64 位输出的串行访问 — 在 FPGA 目标不适合暴露完整 64 位接口时非常有用。

## 项目结构

```

src/ RTL implementation (des_top and submodules, optional wrapper)

tb/ Verification environment (module-level and top-level testbenches)

sim/ ModelSim simulation scripts

docs/ Reports, presentation, architecture diagrams, test vector tooling

```

## 项目演示

设计、架构与实现流程的完整概述可在项目演示中查看:

[DES 算法演示(PDF)](docs/DES_Algorithm_Presentation.pdf)

## 项目背景

作为课程 **“密码算法与 Verilog 实现”** 的一部分。该作业要求在 Verilog 中实现 DES 并展示完整的数字设计流程,包括 RTL 仿真、综合、布局布线与后布线时序仿真。

使用 AI 工具生成初始 RTL 代码。生成的代码经常不完整或错误,需要大量手动工作:调试功能错误、修复逻辑、解决集成问题,并独立构建完整的验证基础设施。

## 致谢

由 Runi Zukerman 与 David Orlian 开发。

标签:Artix-7, DES, Feistel网络, FPGA, Python自动化, RTL设计, S盒替换, Verilog, 位级调试, 初始置换, 参考向量验证, 密钥调度, 循环展开, 数字设计流程, 数据加密标准, 时序验证, 最终置换, 测试平台, 硬件加密, 综合, 逆向工具