jovanbulck/sgx-step

GitHub: jovanbulck/sgx-step

一个用于在Intel SGX飞地上进行指令级单步执行控制的攻击框架,支持页表操作和APIC定时器中断以实现精确的侧信道攻击研究。

Stars: 473 | Forks: 92

# 精准飞地执行控制的实用攻击框架 [](https://github.com/jovanbulck/sgx-step/actions/workflows/ci.yaml)

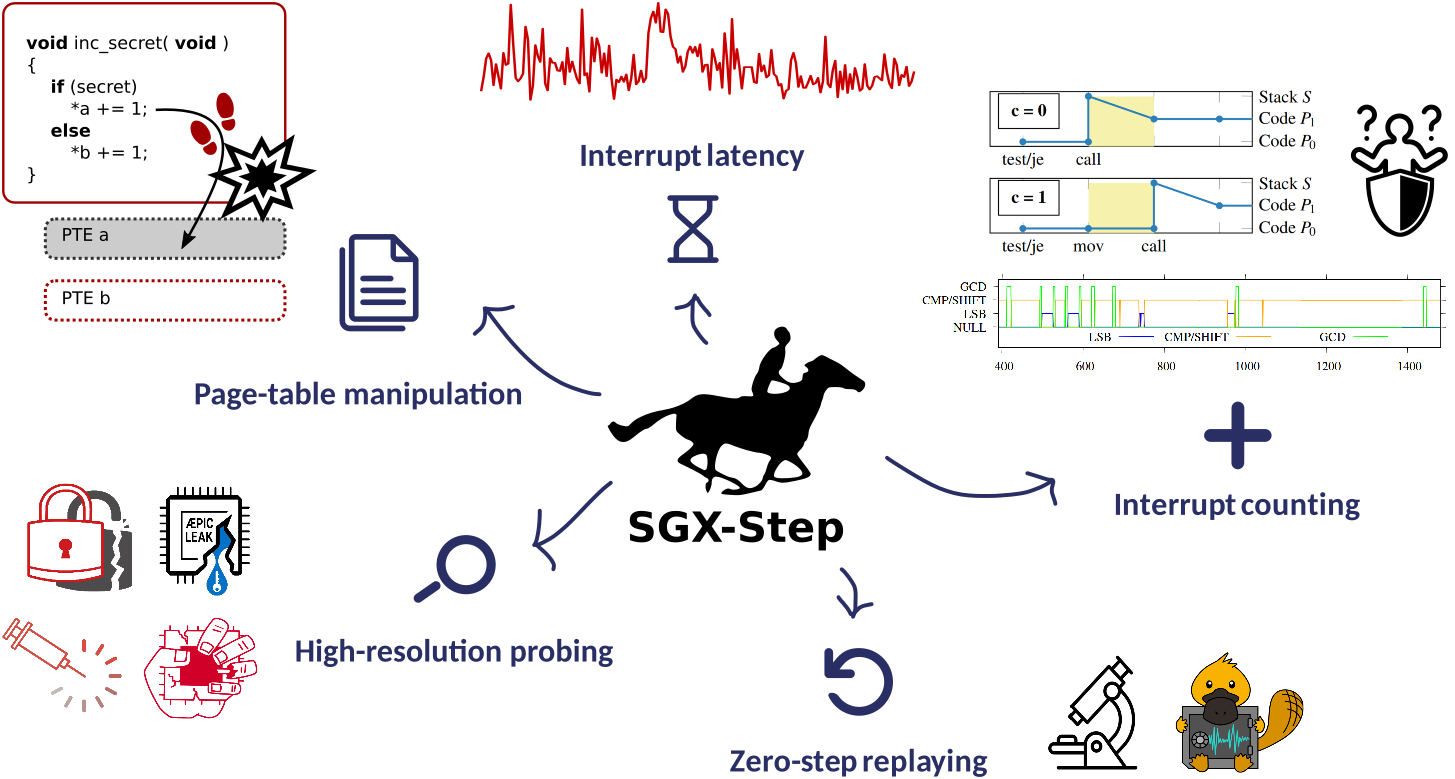

SGX-Step 是一个开源框架,用于促进 Intel x86 处理器(尤其是 Intel SGX 平台)的侧信道攻击研究。

SGX-Step 由一个对抗性 Linux 内核驱动程序和一个小型用户空间操作系统库组成,允许完全从用户空间配置不受信任的页表条目和/或 x86 APIC 定时器中断。SGX-Step 已被我们的研究以及独立研究人员所利用,实现了多个新的和改进的飞地执行攻击,能够以最高的时间分辨率收集侧信道观察结果(即,在受害飞地执行_每一条_指令后进行中断)。

**许可证。** SGX-Step 是免费软件,采用 [GPLv3](https://www.gnu.org/licenses/gpl-3.0) 许可证。SGX-Step 的标志来源于 Eadweard Muybridge 著名的[公有领域](https://en.wikipedia.org/wiki/Sallie_Gardner_at_a_Gallop)"Sallie Gardner at a Gallop"照片系列,与我们的飞地单步执行目标相似,将奔跑的马动态分解为一系列单独的照片帧,以揭示整体的马步态特性。

| SGX-Step 版本 | 变更日志功能 |

| -------------- | ------------------------------------------------------------------------------ |

| v1.5.0 | 稳定化修复(KPTI,内核 ISR 映射);(实验性)Gramine 移植;IPI 支持。 |

| v1.4.0 | 特权中断/调用门(Plundervolt)。 |

| v1.3.0 | 瞬态执行支持(Foreshadow)。 |

| v1.2.0 | 用户空间中断处理和确定性零步过滤(Nemesis)。 |

| v1.1.0 | IA32 支持。 |

| v1.0.0 | 用户空间页表操作和 APIC 定时器单步执行。 |

**出版物。** SGX-Step 已被多个独立研究小组采用,并开创了一系列高分辨率 SGX 攻击。使用 SGX-Step 的已知项目完整最新列表包含在本文档[底部](#bottom)。原始论文的副本可在[此处](https://jovanbulck.github.io/files/systex17-sgxstep.pdf)获取。

```

@inproceedings{vanbulck2017sgxstep,

title = {{SGX-Step}: A Practical Attack Framework for Precise Enclave Execution Control},

author = {Van Bulck, Jo and Piessens, Frank and Strackx, Raoul},

booktitle = {2nd Workshop on System Software for Trusted Execution {(SysTEX)}},

publisher = {{ACM}},

pages = {4:1--4:6},

month = Oct,

year = 2017,

}

```

**演示。** [app/memcmp](app/memcmp) 目录包含一个演示应用程序,通过单步执行一个包含微妙、非恒定时间 `memcmp` 密码比较逻辑的示例飞地来说明 SGX-Step 攻击的威力。与传统的、臭名昭著的噪声时序攻击不同,SGX-Step 可以_线性_时间确定性逐字符暴力破解密码:

## 概述

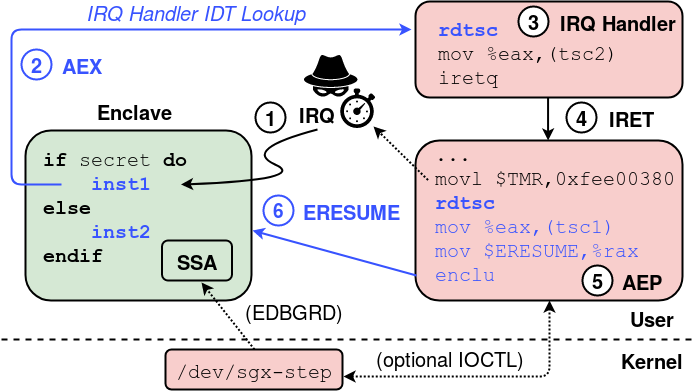

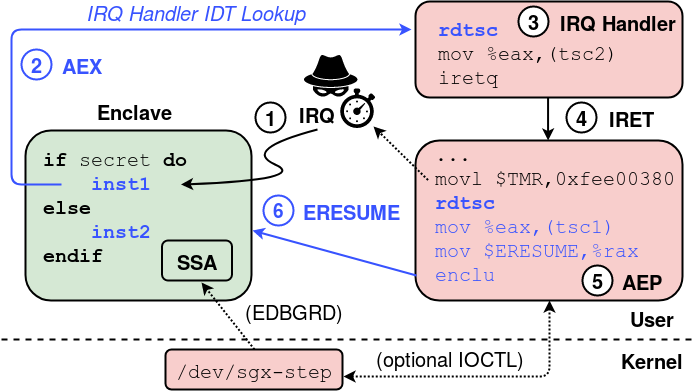

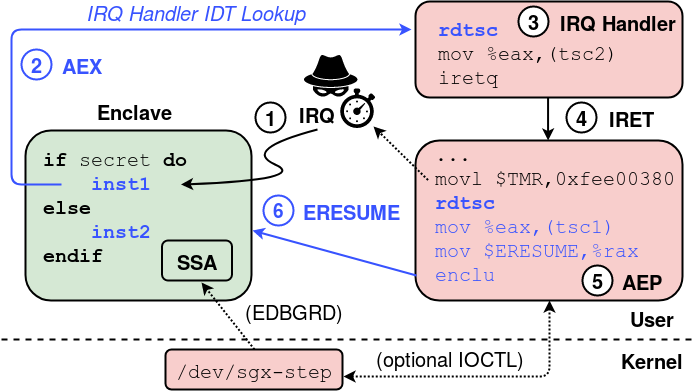

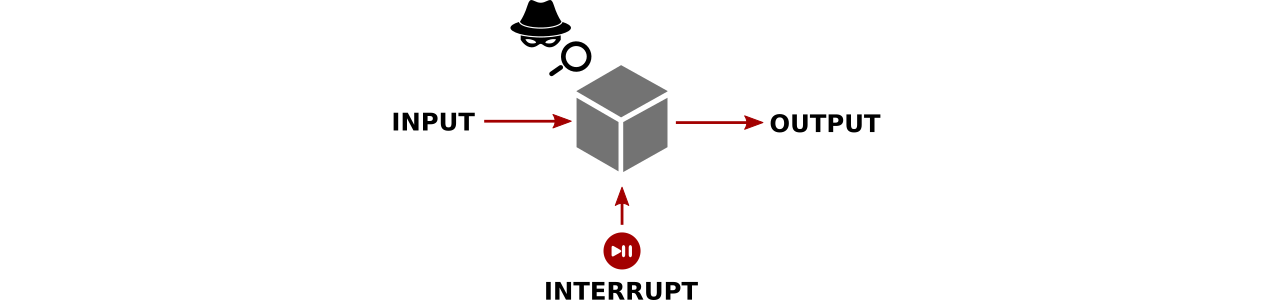

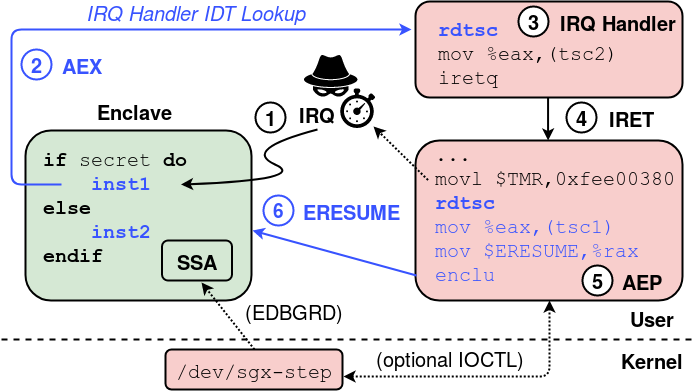

与之前的飞地抢占提案相比,SGX-Step 设计的关键在于为保存页表条目的物理内存位置、本地 APIC 内存映射 I/O 配置寄存器以及 x86 中断描述符表(IDT)创建用户空间虚拟内存映射。这允许一个不受信任的、攻击者控制的主机进程轻松地 (i) 跟踪或修改飞地页表条目,(ii) 配置 APIC 定时器单次/周期性中断源,(iii) 触发处理器间中断,以及 (iv) 完全在_用户空间_注册自定义中断处理程序。

上图总结了我们通过框架中断和恢复 SGX 飞地的硬件和软件步骤序列。

1. 本地 APIC 定时器中断在飞地指令内到达。

2. 处理器执行 AEX procedure,将执行上下文安全存储在飞地的 SSA 帧中,初始化 CPU 寄存器,并跳转到 IDT 中注册的用户空间中断处理程序。

3. 此时,任何特定于攻击的间谍代码都可以轻松插入。

4. 库返回到用户空间 AEP 蹦床。我们修改了官方 SGX SDK 的不受信任运行时,以允许轻松注册自定义 AEP 存根。此外,为了在攻击者控制的基准调试飞地上精确评估我们的方法,SGX-Step 可以_可选地_被检测以从被中断飞地的 SSA 帧中检索存储的指令指针(使用 Linux 的 `/proc/self/mem` 接口和 `EDBGRD` 指令)。

5. 之后,我们在执行 (6) `ERESUME` 之前,通过写入初始计数内存映射 I/O 寄存器来为下一次中断配置本地 APIC 定时器。

## 源代码概述

本仓库组织如下:

```

.

├── app -- Collection of sample client applications using SGX-Step to

│ attack different victim enclave scenarios.

├── doc -- Papers and reference material.

├── kernel -- Minimal dynamically loadable Linux kernel driver to export

│ physical memory to user space and bootstrap `libsgxstep`.

├── libsgxstep -- Small user-space operating system library that implements the

│ actual SGX-Step functionality, including x86 page-table and

│ APIC timer manipulations.

└── sdk -- Bindings to use SGX-Step with different SGX SDKs and libOSs.

```

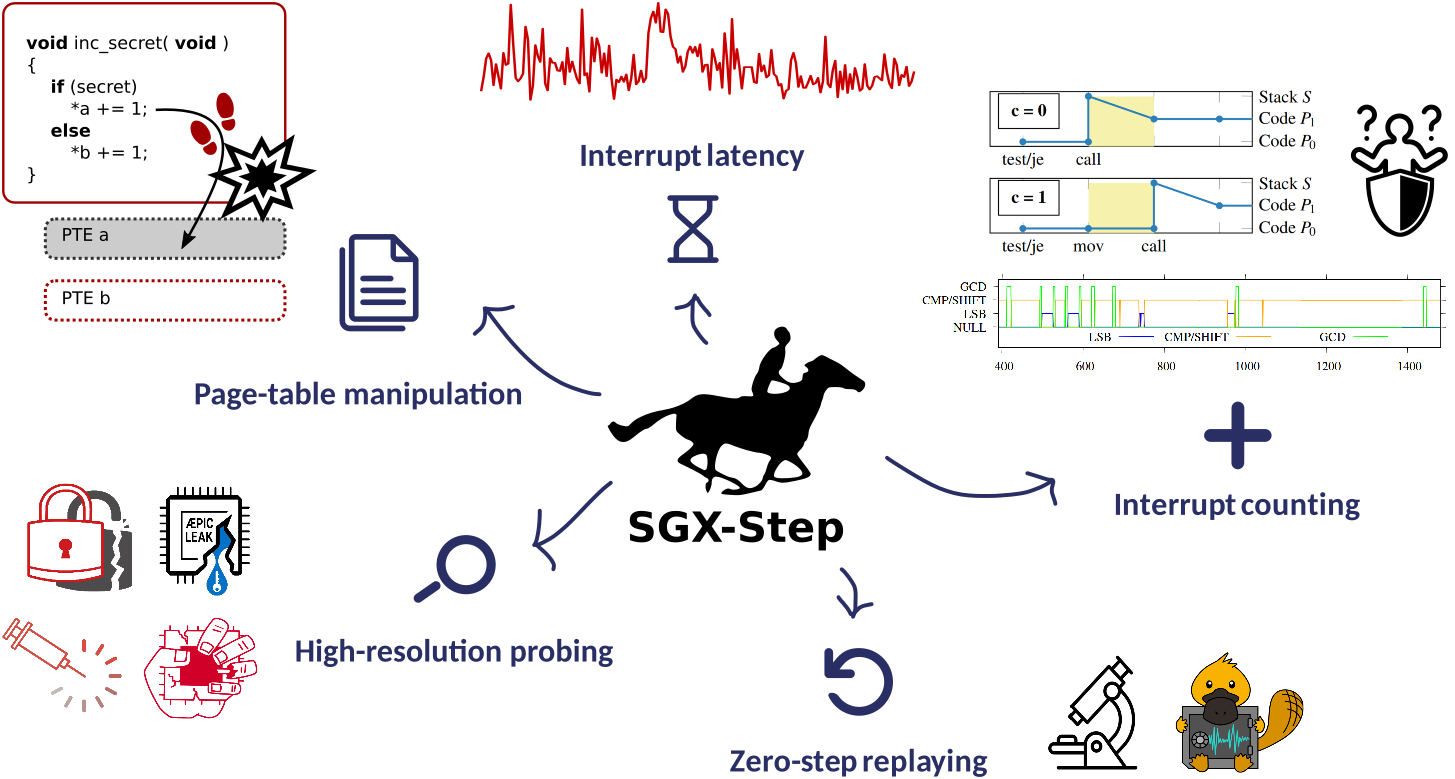

## 框架功能和应用

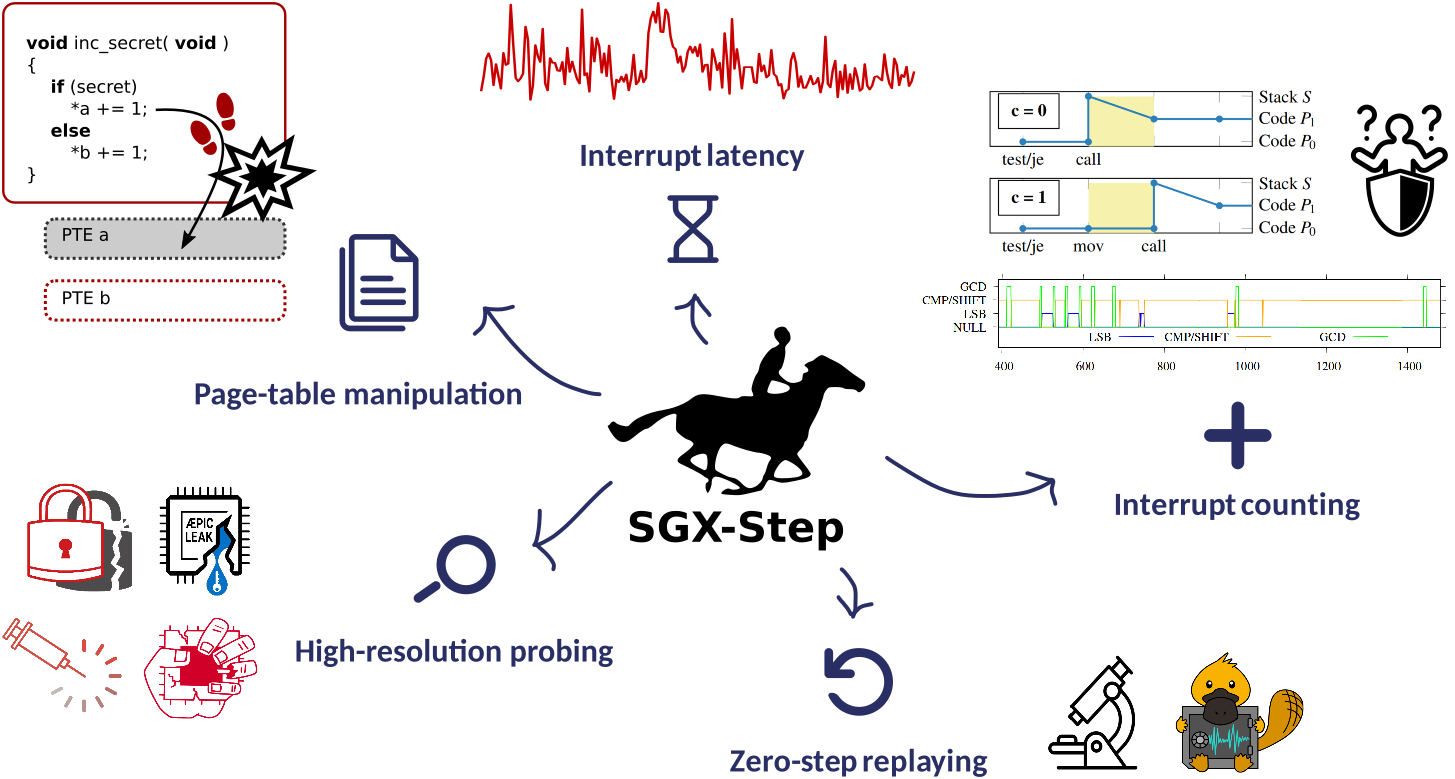

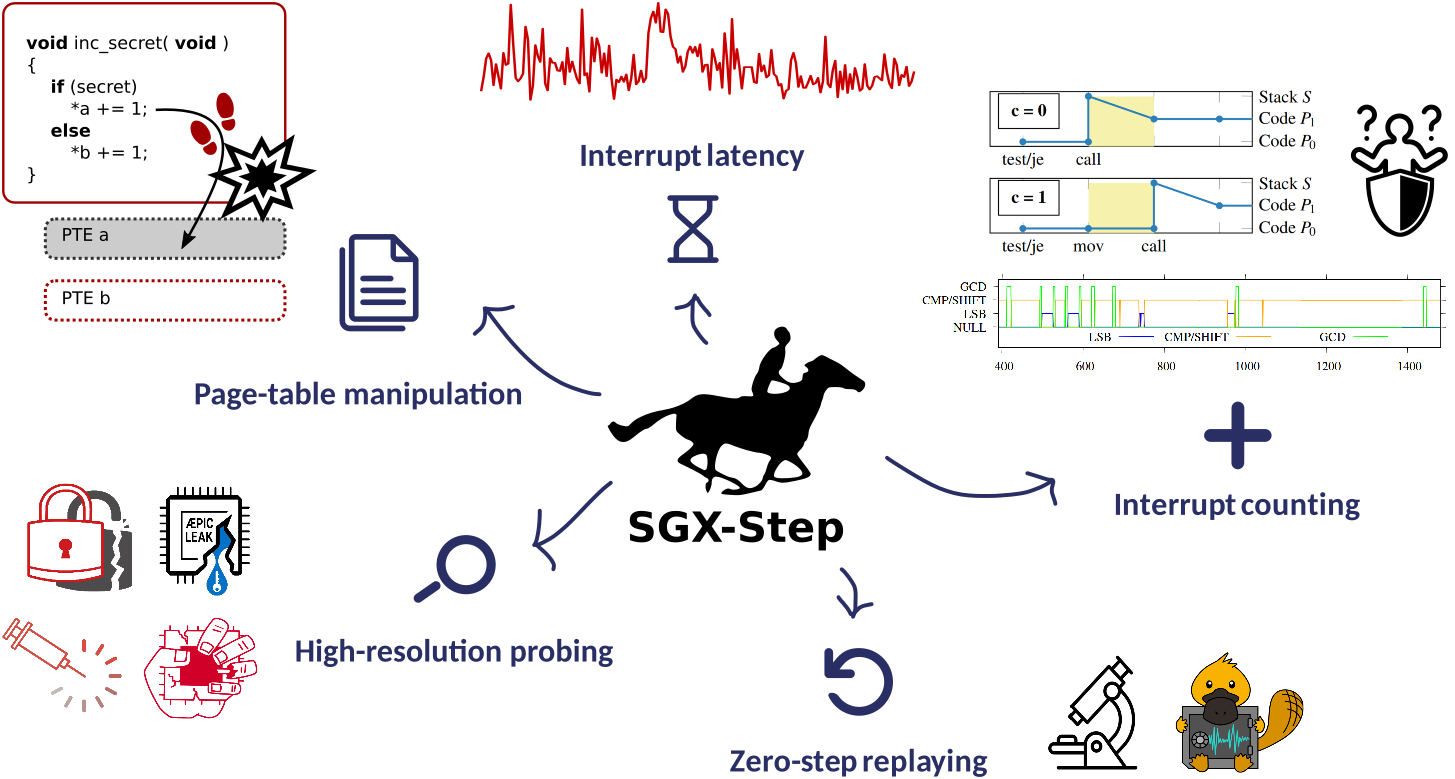

SGX-Step 是一个通用执行控制框架,能够以_任意_攻击者代码精确地交错受害飞地指令。SGX-Step 框架的一些主要用例总结在下图中(另请参阅本文档[底部](#bottom)的使用 SGX-Step 的出版物最新列表)。

## 构建和运行

### 0. 系统要求

SGX-Step 需要支持 [SGX](https://github.com/ayeks/SGX-hardware) 的 Intel 处理器和现成的 Linux 内核。我们的原始评估是在 i7-6500U/6700 CPU 上进行的,运行 Ubuntu 18.04 和标准 Linux 4.15.0 内核。也支持更新的 Linux 内核和发行版。

我们在下面总结了 Linux [内核参数](https://www.kernel.org/doc/html/latest/admin-guide/kernel-parameters.html)。

| Linux 内核参数 | 动机 |

| ------------------------------------ | ------------------------------------------------------------------------------------------------------------------------------------------------------------------------------ |

| `nox2apic` | 可选配置本地 APIC 设备为内存映射 I/O 模式(以使用 SGX-Step 的精确单步执行功能)。如果设置此参数,请确保在 libsgxstep/config.h 中将 X2APIC 设置为 0。或者,您可以让 CPU 保持在 x2APIC 模式,最近的 SGX-Step 发行版也应该兼容。 |

| `iomem=relaxed no_timer_check` | 抑制内核日志中不需要的警告消息。 |

| `nmi_watchdog=0` | 抑制内核 NMI 看门狗。 |

| `isolcpus=1` | 将受害进程绑定到隔离的 CPU 核心。 |

| `clearcpuid=308,295,514` | 禁用监督模式访问预防(SMAP,位 295)、监督模式执行预防(SMEP,位 308)和用户模式指令预防(UMIP,位 514)功能。 |

| `pti=off` | 禁用内核页表隔离(以避免用户 IRQ 处理程序导致内核崩溃)。 |

| `rcupdate.rcu_cpu_stall_suppress=1` | 禁用内核的读-复制更新(RCU)CPU 停滞检测器(以避免长时间单步执行而不调用内核定时器中断处理程序时产生警告。) |

| `msr.allow_writes=on` | 抑制 SGX-Step 对模型特定寄存器(MSR)写入的内核警告消息。 |

| `vdso=0` | 仅在最近的 Linux 内核上:禁用 vdso_sgx_enter_enclave 库(与 AEP 拦截补丁不兼容)。 |

| `dis_ucode_ldr` | 可选禁用 CPU 微码更新(最近的瞬态执行攻击缓解可能需要重新校准单步执行间隔)。 |

按如下方式将所需的启动参数传递给内核:

```

# if you don't have vim, use nano instead

$ sudo vim /etc/default/grub

# Add the following line: GRUB_CMDLINE_LINUX_DEFAULT="quiet splash iomem=relaxed no_timer_check clearcpuid=308,295,514 pti=off isolcpus=1 nmi_watchdog=0 rcupdate.rcu_cpu_stall_suppress=1 msr.allow_writes=on vdso=0"

$ sudo update-grub && reboot

```

要检查当前运行的内核配置是否正确,请执行:

```

$ sudo ./check_sys.sh

.. Checking recommended SGX-Step parameters [OK]

.. Checking unknown kernel parameters [OK]

.. Checking CPU features [OK]

.. Checking kernel page-table isolation [OK]

```

最后,为了提高整体执行时间稳定性,您可以选择在 BIOS 配置中禁用 C-States 和 SpeedStep 技术。

### 1. 构建和加载 `/dev/sgx-step`

SGX-Step 带有一个可加载内核模块,向 `libsgxstep` 用户空间库导出 IOCTL 接口。驱动程序主要负责 (i) 挂钩 APIC 定时器中断处理程序,(ii) 收集不受信任的页表映射,以及 (iii) 可选地获取被中断的基准飞地的指令指针。

要构建和加载 `/dev/sgx-step` 驱动程序,请执行:

```

$ cd kernel/

$ ./install_SGX_driver.sh # tested on Ubuntu 20.04/22.04

$ make clean load

```

**注意(/dev/sgx_enclave)。** SGX-Step 支持传统 Intel `/dev/isgx` 树外驱动程序(应该适用于所有平台),以及适用于具有最新 Linux 内核 >5.11 且支持灵活启动控制的平台的树内 `/dev/sgx_enclave` 驱动程序。`install_SGX_driver.sh` 脚本应自动检测树内 `/dev/sgx-enclave` 驱动程序是否可用,如果不可用,则通过指向未修改的 v2.14 [linux-sgx-driver](_URL_9/>) 的 git 子模块构建和加载树外 `/dev/isgx` 驱动程序。

**注意(/dev/mem)。** 我们依赖 Linux 的虚拟 `/dev/mem` 设备来构建 APIC 物理内存映射 I/O 寄存器和感兴趣页表条目的用户级虚拟内存映射。然而,最近的 Linux 发行版通常启用 `CONFIG_STRICT_DEVMEM` 选项来阻止这种使用。因此,我们的 `/dev/sgx-step` 驱动程序包含一种[方法](https://www.libcrack.so/index.php/2012/09/02/bypassing-devmem_is_allowed-with-kprobes/)来绕过 `devmem_is_allowed` 检查,而无需重新编译内核。

### 2. 补丁和安装 SGX SDK

为了轻松注册自定义异步退出指针(AEP)存根,我们修改了官方 Intel SGX SDK 的不受信任运行时。按以下步骤检出 [linux-sgx](https://github.com/01org/linux-sgx) v2.23 并应用我们的补丁。

```

$ cd sdk/intel-sdk/

$ ./install_SGX_SDK.sh # tested on Ubuntu 20.04/22.04

$ source /opt/intel/sgxsdk/environment # add to ~/.bashrc to preserve across terminal sessions

$ sudo service aesmd status # stop/start aesmd service if needed

```

上述安装脚本已在 Ubuntu 22.04 LTS 上测试。

对于其他 GNU/Linux 发行版,请按照 [linux-sgx](https://github.com/01org/linux-sgx) 项目中的说明构建和安装 Intel SGX SDK 和 PSW 包。您还需要构建和加载一个(未修改的)[linux-sgx-driver](https://github.com/01org/linux-sgx-driver) SGX 内核模块才能使用 SGX-Step。

**注意(本地安装)。** 补丁 SGX SDK 和 PSW 包可以本地安装,而不会影响兼容的系统级 'linux-sgx' 安装。为此,示例 Makefile 支持指向本地 SDK 安装目录的 `SGX_SDK` 环境变量。当检测到非默认 SDK 路径(即不是 `/opt/intel/sgxsdk`)时,"run" Makefile 目标还会动态链接到本地 `linux-sgx` 目录中构建的补丁 `libsgx_urts.so` 不受信任运行时(使用 `LD_LIBRARY_PATH` 环境变量)。

**注意(32 位支持)。** 构建 32 位版本 SGX SDK 和 SGX-Step 的说明(已过时且未维护!)可在 [README-m32.md](README-m32.md) 中找到。

### 3. 构建和运行测试应用程序

用户空间应用程序可以链接到 `libsgxstep` 库以使用 SGX-Step 的单步执行和页表操作功能。请查看 "app" 目录中的示例应用程序。

首先,检查 APIC 和中断描述符表设置:

```

$ cd app/selftest/idt

$ make run # fires interrupts in an infinite loop to stress-test stability; exit with CTRL-C

```

例如,要构建和运行一个测试页表操作功能和 SDK 补丁的基本示例应用程序:

```

$ cd app/aep-redirect

$ make run

```

要测试定时器单步执行功能,可以尝试构建和运行一个基准飞地来单步执行 100 个连续的 `nop` 指令:

```

$ cd app/bench

$ NUM=100 make parse # alternatively vary NUM and use STRLEN=1 or ZIGZAG=1

```

上述命令构建 `libsgxstep`、基准受害飞地和不受信任的攻击者主机进程,其中攻击场景和实例大小通过相应的环境变量配置。该命令还非交互式运行生成的二进制文件(以确保确定性定时器间隔),最后调用特定于攻击的后处理 Python 脚本来解析生成的飞地指令指针基准结果。

**注意(性能)。** 单步执行飞地执行会产生相当大的减速。我们测量到论文中描述的实验执行时间长达 15 分钟。SGX-Step 的页表操作功能允许仅对选定函数启动单步执行,例如通过撤销特定感兴趣代码或数据页的访问权限。

**注意(定时器间隔)。** 确切的定时器间隔值取决于 CPU 频率,因此本质上仍然是平台特定的(另请参阅 [app/selftest/apic](app/selftest/apic) 了解评估各种 APIC 定时器模式准确性的详细微基准测试)。在 `/app/bench/main.c` 中配置合适的值。我们通过调整和观察 NOP 微基准测试飞地指令指针跟踪结果,为我们的评估平台确定了精确的定时器间隔(见下表),如下所述。

**注意(稳定性)。** 为了避免 Linux 内核卡住或崩溃,SGX-Step 应在退出 `libsgxstep` 进程后自动恢复中断描述符表和本地 APIC 定时器。您可以按如下方式检查 APIC 定时器是否仍在所有核心上触发:

```

$ watch -n0.1 "cat /proc/interrupts | grep 'Local timer interrupts'"

```

## 校准单步执行间隔

下表列出了当前支持的 Intel CPU 及其单步执行 APIC 定时器间隔(`libsgxstep/config.h`)。

请注意,确切的单步执行间隔可能取决于处理器的微码版本,当最近的[瞬态执行攻击](https://transient.fail/) 缓解措施在飞地进入/退出时刷新微架构缓冲区时更是如此。下表中提供了一些不同的微码版本作为参考。

| 型号名称 | CPU | 基础频率 | 微码(日期) | APIC 定时器间隔 |

| ------------- | --------------------------------------------------------------------------------------------------------------------------------------- | -------------- | ----------------------- | ------------------- |

| Skylake | [i7-6700](https://ark.intel.com/products/88196) | 3.4 GHz | ? | 19 |

| Skylake | [i7-6500U](https://ark.intel.com/products/88194) | 2.5 GHz | ? | 25 |

| Skylake | [i5-6200U](https://ark.intel.com/products/88193) | 2.3 GHz | ? | 28 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | ? | 34 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | 0xca (2019-10-03) | 54 |

| Coffee Lake R | [i7-9700](https://ark.intel.com/content/www/us/en/ark/products/191792/intel-core-i79700-processor-12m-cache-up-to-4-70-ghz.html) | 3 GHz | 0xf4 (2022-07-31) | 26 |

| Coffee Lake R | [i9-9900K](https://ark.intel.com/products/186605) | 3.6 GHz | ? | 21 |

| Coffee Lake HR | [i7-9750H](https://ark.intel.com/content/www/us/en/ark/products/191045/intel-core-i7-9750h-processor-12m-cache-up-to-4-50-ghz.html) | 2.6 GHz | 0xf4 (2023-02-23) | 37 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0x32 (2019-07-05) | 135 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0xb0 (2022-03-09) | 255 |

| Comet Lake | [i9-10900K](https://www.intel.com/content/www/us/en/products/sku/199332/intel-core-i910900k-processor-20m-cache-up-to-5-30-ghz.html) | 3.70 GHz | 0xfc (2024-02-01) | 24 |

| Emerald Rapids | [Xeon Gold 5515+](https://ark.intel.com/content/www/us/en/ark/products/237562/intel-xeon-gold-5515-processor-22-5m-cache-3-20-ghz.html) | 3.2 GHz | 0x21000230 (2024-02-05) | 32 |

**注意(校准)。**

目前,配置可靠定时器间隔的最简单方法是使用 `app/bench` 基准测试工具和长 NOP 滑动,并逐渐增加/减少 `SGX_STEP_TIMER_INTERVAL`。您可以从大约 20 开始,然后执行 `NUM=100 make parse` 来获取 100 条指令 NOP 滑动的单步、零步和多步摘要(一旦您有了更稳定的间隔,您可以切换到更长的滑动)。零步太多表明您需要增加定时器间隔,而多步则需要降低定时器间隔。

**注意(过滤零步)。**

重要提示:当剩下一些零步时不要担心,只要您取得进展,您可以通过查看飞地的代码 PTE 访问位(该位仅在指令实际退休并发生单步时设置)来确定性地过滤掉零步。因此,在配置了保守的定时器间隔以始终避免多步之后,SGX-Step 可以实现_完美的_指令级粒度的无噪声单步执行。

**注意(扩展中断"着陆窗口")。**

如下面的根本原因分析所阐明的,解析 `ERESUME` 后第一个飞地指令(代码)地址的页表遍历越慢,中断"着陆窗口"就越长,因此 SGX-Step 的单步执行可靠性就越高。例如,我们发现,除了清除飞地的 PMD 访问位之外,通过在 `ERESUME` 之前从 CPU 缓存刷新一个或多个不受保护的页表条目,可以进一步扩展着陆窗口,迫使 CPU 在页表遍历期间等待慢速内存。因此,当您找不到可靠的定时器间隔配置时,请确保 (i) 清除飞地的代码 PTE/PMD "访问"位,(ii) 在 AEP 处理程序中刷新(`CLFLUSH`)一个或多个飞地页表条目。

**注意(微码)。**

另一个警告涉及最近的 Foreshadow/ZombieLoad/RIDL/etc 微码缓解措施,这些措施在飞地进入/退出时刷新易受攻击的 uarch 缓冲区。请注意,当启用这些缓解措施时,定时器间隔将需要增加,因为飞地进入需要更长时间(例如,在我 的 i7-8650U CPU 上,我发现单步定时器间隔上升到 54,而使用 Foreshadow 之前的微码仅为 34)。

额外的刷新操作可能还会增加飞地进入时间的方差,这意味着您可能需要更保守地配置定时器,并允许更多零步(可以如上所述确定性地过滤掉)。

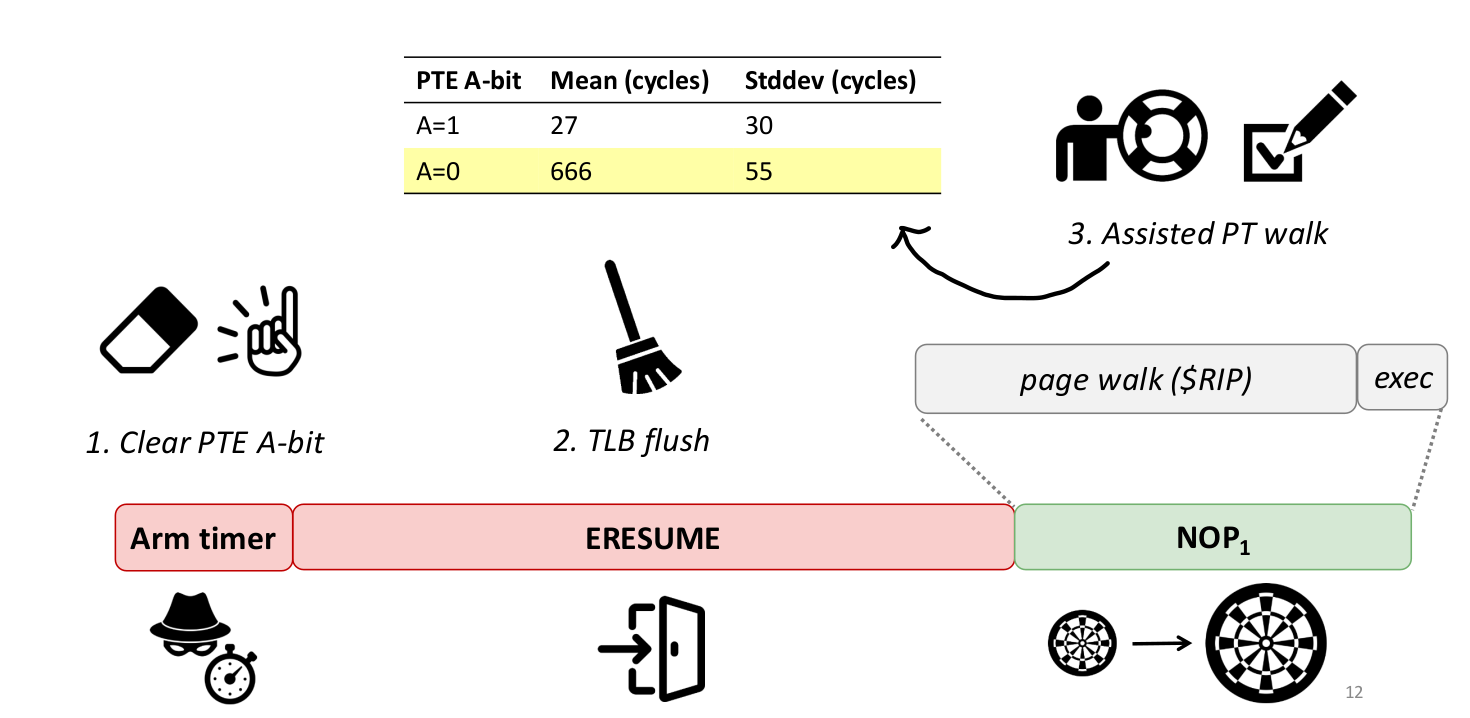

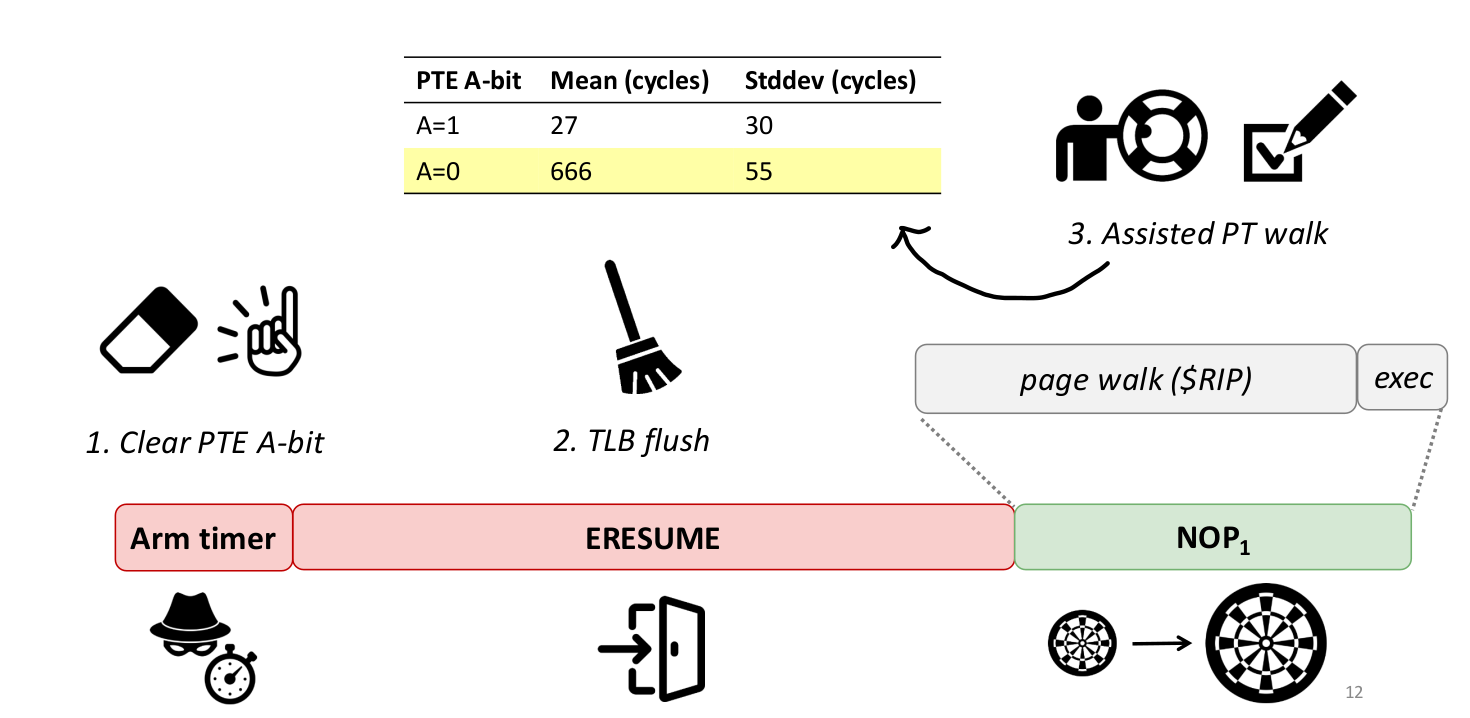

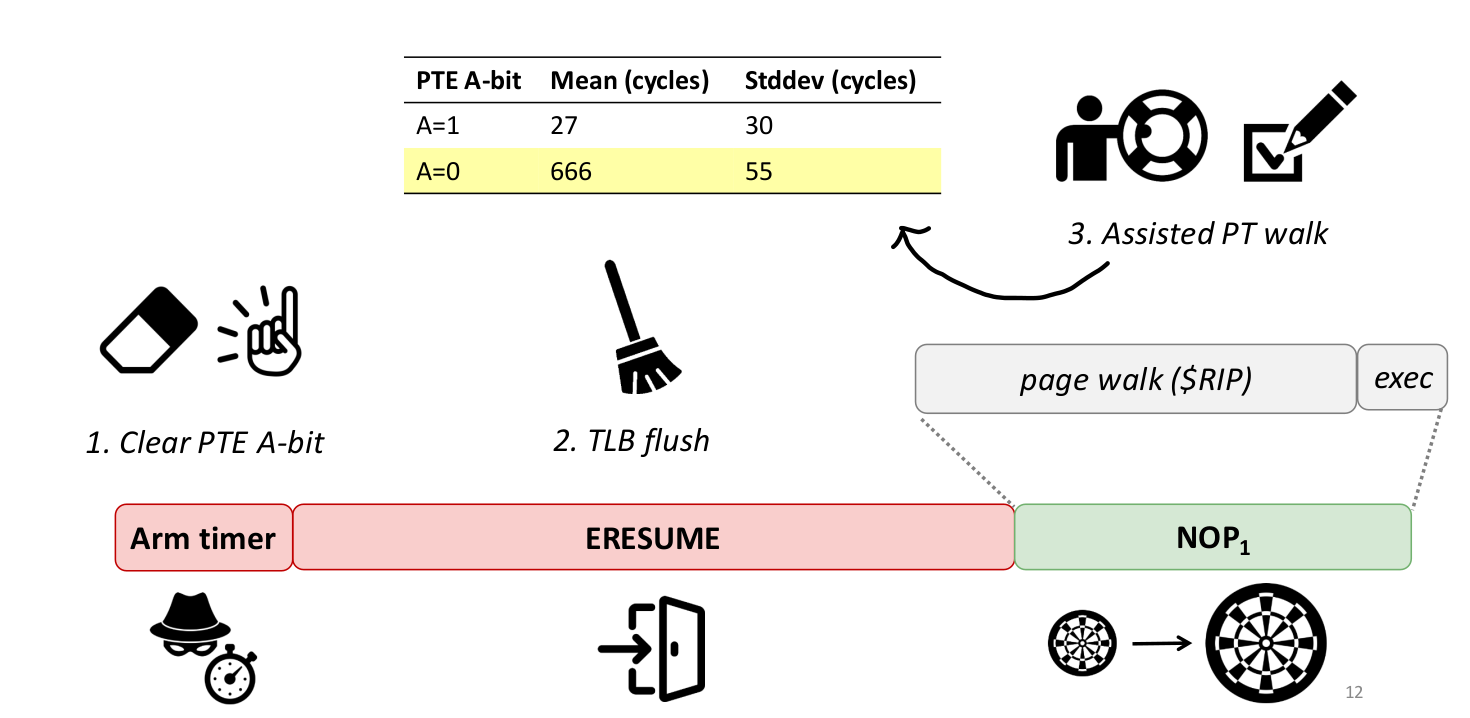

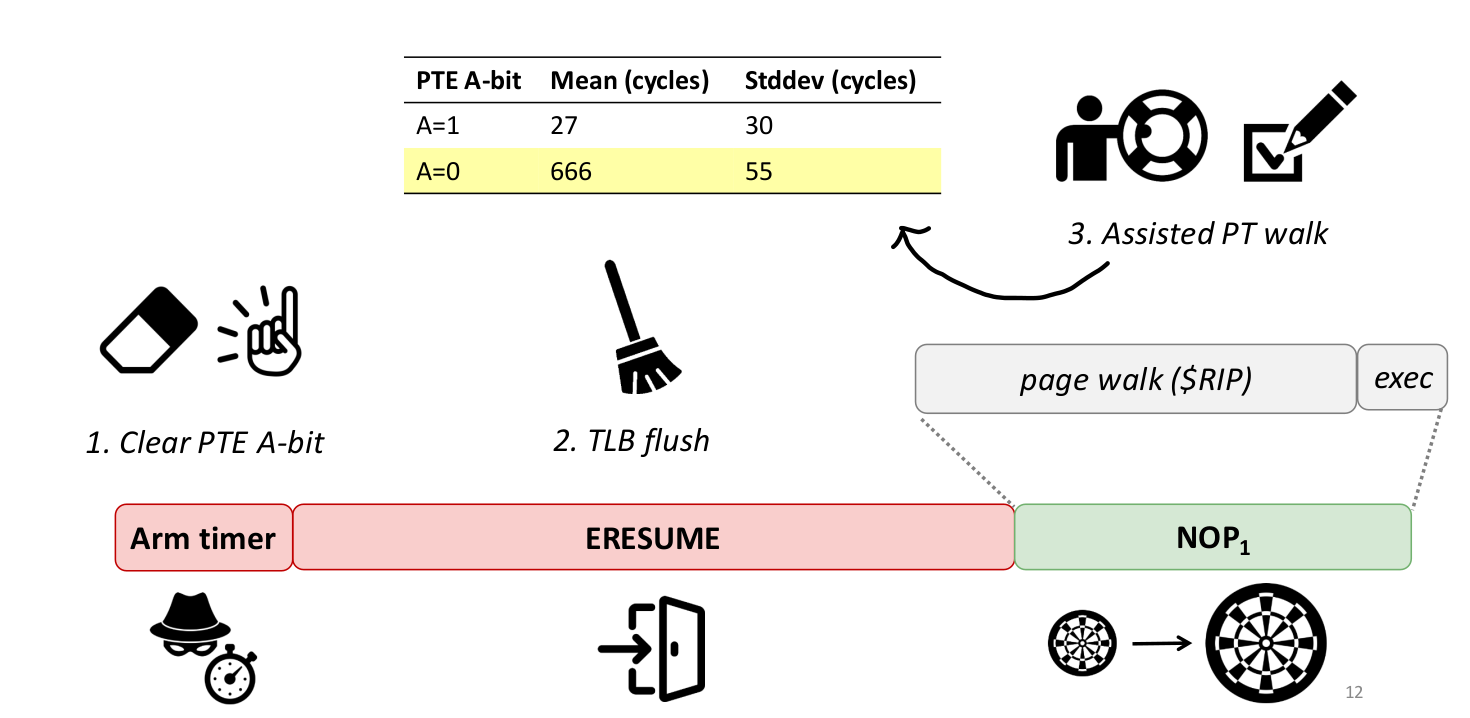

### SGX-Step 根本原因分析

关于 SGX-Step 如何可靠地中断臭名昭著复杂的 `ERESUME` 指令之后的第一个(可能非常短的!)飞地指令的详细根本原因分析在 [AEX-Notify](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) 论文中有描述。

我们发现 SGX-Step 成功的关键在于使用"访问"(A) 位。具体来说,SGX-Step 在配置 APIC 触发单次中断之前,始终清除受害飞地页中间目录(PMD)中的 A 位。A 位仅在飞地至少执行一条指令时才会被处理器设置,因此可用于确定性地区分零步和单步。

关键的是,由于处理器的页未命中处理程序针对常见的快速路径进行了优化,并使用慢得多的"微码辅助"来处理不太频繁且更复杂的需要修改 PMD 或 PTE 的情况,这种辅助的效果是将 `ERSUME` 后的第一个飞地指令的执行延长数百个周期。因此,这个"辅助窗口"为粗粒度的、通常分布式的 APIC 定时器中断提供了宽敞的着陆空间,使其能够高精度到达。

## 在您自己的项目中使用 SGX-Step

在您自己的项目中开始使用 SGX-Step 框架的最简单方法是通过 [git 子模块](https://git-scm.com/book/en/v2/Git-Tools-Submodules):

```

$ cd my/git/project

$ git submodule add https://github.com/jovanbulck/sgx-step.git

$ cd sgx-step # Now build `/dev/sgx-step` and `libsgxstep` as described above

```

请查看 `app` 目录中的 Makefile,了解客户端应用程序如何链接到 `libsgxstep` 以及任何本地 SGX SDK/PSW 包。

以下是使用 SGX-Step 的已知项目列表。如果您的项目使用了 SGX-Step 但未包含在下面,请随时提交拉取请求。

| 标题 | 出版物详情 | 源代码 | 使用的 SGX-Step 功能 |

| ---------------------------------------------------------------------------------------------- | -------------------------------------------------------------------------------------------- | ------------------------------------------------------------------------- | ------------------------------------------------------- |

| AEX-NStep: Probabilistic Interrupt Counting Attacks on Intel SGX | [S&P'26](https://arxiv.org/pdf/2510.14675) | [Zenodo](https://zenodo.org/records/17338383) | Page faults, IPIs, WRMSR Interrupt Gate |

| MDPeek: Breaking Balanced Branches in SGX with Memory Disambiguation Unit Side Channels | [ASPLOS'25](https://www.comp.nus.edu.sg/~tcarlson/pdfs/liu2025mbbbiswmdusc.pdf) | [GitHub (Artifact Evaluated & Functional)](https://github.com/CPU-THU/MDPeek) | Page faults |

| Activation Functions Considered Harmful: Recovering Neural Network Weights through Controlled Channels | [ArXiv'25](https://arxiv.org/pdf/2503.19142) | - | Single-stepping, PTE A/D |

| TLBlur: Compiler-Assisted Automated Hardening against Controlled Channels on Off-the-Shelf Intel SGX Platforms | [USEC'25](https://vanbulck.net/files/usenix25-tlblur.pdf) | [GitHub (full)](https://github.com/TLBlur-SGX) | Single-stepping, PTE A/D, page faults |

| POSTER: On the Feasibility of Inferring SGX Execution through PMU | [AsiaCCS'24](https://dl.acm.org/doi/pdf/10.1145/3634737.3659434) | - | Single-stepping, zero-stepping|

| SIGY: Breaking Intel SGX Enclaves with Malicious Exceptions & Signals | [ArXiv'24](https://arxiv.org/abs/2404.13998) | - | Timer interrupts, page faults |

| On (the Lackin) Code Confidentiality in Trusted Execution Environments | [S&P24](https://ivanpuddu.com/files/papers/TEE_WASM_code_Leakage.pdf) | [GitHub (empty)](https://github.com/dn0sar/TEE-WASM-Code-Extraction) | Single-stepping |

| TeeJam: Sub-Cache-Line Leakages Strike Back | [CHES24](https://doi.org/10.46586/tches.v2024.i1.457-500) | [Github (full)](https://github.com/UzL-ITS/teejam) | Single-stepping interrupt latency, PTE A/D |

| AEX-Notify: Thwarting Precise Single-Stepping Attacks through Interrupt Awareness for Intel SGX Enclaves | [USEC23](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) | [GitHub (SGX SDK mitigation)](https://github.com/intel/linux-sgx/blob/master/sdk/trts/linux/trts_mitigation.S) | Single-Stepping, PTE A/D

| Controlled Data Races in Enclaves: Attacks and Detection | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-chen-sanchuan.pdf) | [GitHub (non-attack)](https://github.com/OSUSecLab/SGXRacer) | Single-stepping, APIC |

| BunnyHop: Exploiting the Instruction Prefetcher | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-zhang-zhiyuan-bunnyhop.pdf) | [GitHub (non-SGX PoC)](https://github.com/0xADE1A1DE/BunnyHop) | Single-stepping, PTE A/D |

| Downfall: Exploiting Speculative Data Gathering | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-moghimi.pdf) | [GitHub (non-SGX PoC)](https://github.com/flowyroll/downfall/tree/main/POC) | Single-stepping, zero-stepping |

| All Your PC Are Belong to Us: Exploiting Non-control-Transfer Instruction BTB Updates for Dynamic PC Extraction | [ISCA23](https://dl.acm.org/doi/pdf/10.1145/3579371.3589100?casa_token=Q5jf5nOgiLIAAAAA:cT0ltJh7vk943buODuR4oMFKmuhg2Tp-djFm2kUu6DzlxtBhNhEw2WteRggn0k99D7ft-P6pluVrFA) | - | Single-stepping |

| Cache-timing attack against HQC | [CHES23](https://eprint.iacr.org/2023/102.pdf) | - | Single-stepping, PTE A/D |

| FaultMorse: An automated controlled-channel attack via longest recurring sequence | [ComSec23](https://www.sciencedirect.com/science/article/pii/S0167404822003959) | [GitHub (post processing)](https://github.com/Ezekiel-1998/FaultMorse) | Page fault |

| AEPIC Leak: Architecturally Leaking Uninitialized Data from the Microarchitecture | [USEC22](https://www.usenix.org/system/files/sec22-borrello.pdf) | [GitHub (full)](https://github.com/IAIK/AEPIC) | Single-Stepping, PTE A/D |

| MoLE: Mitigation of Side-channel Attacks against SGX via Dynamic Data Location Escape | [ACSAC22](https://dl.acm.org/doi/fullHtml/10.1145/3564625.3568002) | - | Single-Stepping, page fault, transient execution |

| WIP: Interrupt Attack on TEE-Protected Robotic Vehicles | [AutoSec22](https://www.ndss-symposium.org/wp-content/uploads/autosec2022_23001_paper.pdf) | - | Single-stepping, multi-stepping |

| Towards Self-monitoring Enclaves: Side-Channel Detection Using Performance Counters | [NordSec22](https://link.springer.com/chapter/10.1007/978-3-031-22295-5_7) | - | Page fault, LVI. |

| ENCLYZER: Automated Analysis of Transient Data Leaks on Intel SGX | [SEED22](https://ieeexplore.ieee.org/document/9935016) | [GitHub (full)](https://github.com/bloaryth/enclyser) | Page-table manipulation |

| Side-Channeling the Kalyna Key Expansion | [CT-RSA22](https://cs.adelaide.edu.au/~yval/pdfs/ChuengsatiansupGYZ22.pdf) | - | Single-Stepping, PTE A/D |

| Rapid Prototyping for Microarchitectural Attacks | [USENIX22](https://www.usenix.org/system/files/sec22summer_easdon.pdf) | [GitHub (full)](https://github.com/libtea/frameworks) | Single-stepping, page fault, PTE A/D, etc. |

| Util::Lookup: Exploiting Key Decoding in Cryptographic Libraries | [CCS21](https://dl.acm.org/doi/abs/10.1145/3460120.3484783) | [GitHub (full)](https://github.com/UzL-ITS/util-lookup) | Single-Stepping, PTE A/D |

| SmashEx: Smashing SGX Enclaves Using Exceptions | [CCS21](https://dl.acm.org/doi/pdf/10.1145/3460120.3484821) | - | Single-stepping |

| Online Template Attacks: Revisited | [CHES21](https://tches.iacr.org/index.php/TCHES/article/view/8967/8545) | [Zenodo (simulation)](https://zenodo.org/record/4680071) | Single-stepping, page fault, PTE A/D |

| Aion Attacks: Manipulating Software Timers in Trusted Execution | [DIMVA21](http://individual.utoronto.ca/shengjiexu/publication/whuang-dimva2021-aion_v2.pdf) | - | Single-stepping, interrupts(?) |

| Platypus: Software-based Power Side-Channel Attacks on x86 | [S&P21](https://platypusattack.com/platypus.pdf) | [GitHub (simulated PoC)](https://github.com/0xhilbert/Platypus) | Single-stepping, zero-stepping |

| CrossTalk: Speculative Data Leaks Across Cores Are Real | [S&P21](https://download.vusec.net/papers/crosstalk_sp21.pdf) | - | Single-stepping, page fault |

| Frontal Attack: Leaking Control-Flow in SGX via the CPU Frontend | [USEC21](https://www.usenix.org/system/files/sec21-puddu.pdf) | [GitHub (full, artifact evaluated)](https://github.com/dn0sar/frontal_poc) | Single-stepping interrupt latency, PTE A/D |

| PThammer: Cross-User-Kernel-Boundary Rowhammer through Implicit Accesses | - | [MICRO20](https://arxiv.org/pdf/2007.08707v2.pdf) | Page table walk |

| SpeechMiner: A Framework for Investigating andMeasuring Speculative Execution Vulnerabilities | [NDSS20](https://www.ndss-symposium.org/wp-content/uploads/2020/02/23105-paper.pdf) | [GitHub (full)](https://github.com/teecert/SpeechMiner) | Page-table manipulation |

| Déjà Vu: Side-Channel Analysis of Mozilla's NSS | [CCS20](https://dl.acm.org/doi/pdf/10.1145/3372297.3421761) | - | Page fault |

| From A to Z: Projective coordinates leakage in the wild | [CHES20](https://eprint.iacr.org/2020/432.pdf) | - | Page fault |

| LVI: Hijacking Transient Execution through Microarchitectural Load Value Injection | [S&P20](https://lviattack.eu/lvi.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step-lvi/tree/master/app/lvi) | Single-stepping, page-table manipulation |

| CopyCat: Controlled Instruction-Level Attacks on Enclaves | [USEC20](https://arxiv.org/pdf/2002.08437.pdf) | - | Single-stepping, page fault, PTE A/D |

| When one vulnerable primitive turns viral: Novel single-trace attacks on ECDSA and RSA | [CHES20](https://eprint.iacr.org/2020/055.pdf) | - | Single-stepping, page fault, PTE A/D |

| Big numbers - Big Troubles: Systematically Analyzing Nonce Leakage in (EC)DSA Implementations | [USEC20](https://www.usenix.org/system/files/sec20summer_weiser_prepub_0.pdf) | - | Page fault |

| Plundervolt: Software-based Fault Injection Attacks against Intel SGX | [S&P20](https://plundervolt.com/doc/plundervolt.pdf) | [GitHub (full)](https://github.com/KitMurdock/plundervolt) | Privileged interrupt/call gates, MSR |

| Bluethunder: A 2-level Directional Predictor Based Side-Channel Attack against SGX | [CHES20](https://heartever.github.io/files/bluethunder_sgx_ches.pdf) | - | Single-stepping |

| Fallout: Leaking Data on Meltdown-resistant CPUs | [CCS19](https://mdsattacks.com/files/fallout.pdf) | - | PTE A/D |

| A Tale of Two Worlds: Assessing the Vulnerability of Enclave Shielding Runtimes | [CCS19](https://people.cs.kuleuven.be/~jo.vanbulck/ccs19-tale.pdf) | [GitHub (full)](https://github.com/jovanbulck/0xbadc0de) | Single-stepping, page fault, PTE A/D |

| ZombieLoad: Cross-Privilege-Boundary Data Sampling | [CCS19](https://zombieloadattack.com/zombieload.pdf) | [GitHub (PoC)](https://github.com/IAIK/ZombieLoad/) | Single-stepping, zero-stepping, page-table manipulation |

| SPOILER: Speculative Load Hazards Boost Rowhammer and Cache Attacks | [USEC19](https://arxiv.org/pdf/1903.00446.pdf) | - | Single-stepping interrupt latency |

| Nemesis: Studying Microarchitectural Timing Leaks in Rudimentary CPU Interrupt Logic | [CCS18](https://people.cs.kuleuven.be/~jo.vanbulck/ccs18.pdf) | [GitHub (full)](https://github.com/jovanbulck/nemesis) | Single-stepping interrupt latency, page fault, PTE A/D |

| Foreshadow: Extracting the Keys to the Intel SGX Kingdom with Transient Out-of-Order Execution | [USEC18](https://foreshadowattack.eu/foreshadow.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step/tree/master/app/foreshadow) | Single-stepping, zero-stepping, page-table manipulation |

| Single Trace Attack Against RSA Key Generation in Intel SGX SSL | [AsiaCCS18](https://rspreitzer.github.io/publications/proc/asiaccs-2018-paper-1.pdf) | - | Page fault |

| Off-Limits: Abusing Legacy x86 Memory Segmentation to Spy on Enclaved Execution | [ESSoS18](https://people.cs.kuleuven.be/~jo.vanbulck/essos18.pdf) | [link (full, artifact evaluated)](https://distrinet.cs.kuleuven.be/software/off-limits/) | Single-stepping, IA32 segmentation, page fault |

| SGX-Step: A Practical Attack Framework for Precise Enclave Execution Control | [SysTEX17](https://people.cs.kuleuven.be/~jo.vanbulck/systex17.pdf) | [GitHub (full)](https://github.com/jovanbulck/sgx-step/tree/master/app/bench) | Single-stepping, page fault, PTE A/D |

SGX-Step 是一个开源框架,用于促进 Intel x86 处理器(尤其是 Intel SGX 平台)的侧信道攻击研究。

SGX-Step 由一个对抗性 Linux 内核驱动程序和一个小型用户空间操作系统库组成,允许完全从用户空间配置不受信任的页表条目和/或 x86 APIC 定时器中断。SGX-Step 已被我们的研究以及独立研究人员所利用,实现了多个新的和改进的飞地执行攻击,能够以最高的时间分辨率收集侧信道观察结果(即,在受害飞地执行_每一条_指令后进行中断)。

**许可证。** SGX-Step 是免费软件,采用 [GPLv3](https://www.gnu.org/licenses/gpl-3.0) 许可证。SGX-Step 的标志来源于 Eadweard Muybridge 著名的[公有领域](https://en.wikipedia.org/wiki/Sallie_Gardner_at_a_Gallop)"Sallie Gardner at a Gallop"照片系列,与我们的飞地单步执行目标相似,将奔跑的马动态分解为一系列单独的照片帧,以揭示整体的马步态特性。

| SGX-Step 版本 | 变更日志功能 |

| -------------- | ------------------------------------------------------------------------------ |

| v1.5.0 | 稳定化修复(KPTI,内核 ISR 映射);(实验性)Gramine 移植;IPI 支持。 |

| v1.4.0 | 特权中断/调用门(Plundervolt)。 |

| v1.3.0 | 瞬态执行支持(Foreshadow)。 |

| v1.2.0 | 用户空间中断处理和确定性零步过滤(Nemesis)。 |

| v1.1.0 | IA32 支持。 |

| v1.0.0 | 用户空间页表操作和 APIC 定时器单步执行。 |

**出版物。** SGX-Step 已被多个独立研究小组采用,并开创了一系列高分辨率 SGX 攻击。使用 SGX-Step 的已知项目完整最新列表包含在本文档[底部](#bottom)。原始论文的副本可在[此处](https://jovanbulck.github.io/files/systex17-sgxstep.pdf)获取。

```

@inproceedings{vanbulck2017sgxstep,

title = {{SGX-Step}: A Practical Attack Framework for Precise Enclave Execution Control},

author = {Van Bulck, Jo and Piessens, Frank and Strackx, Raoul},

booktitle = {2nd Workshop on System Software for Trusted Execution {(SysTEX)}},

publisher = {{ACM}},

pages = {4:1--4:6},

month = Oct,

year = 2017,

}

```

**演示。** [app/memcmp](app/memcmp) 目录包含一个演示应用程序,通过单步执行一个包含微妙、非恒定时间 `memcmp` 密码比较逻辑的示例飞地来说明 SGX-Step 攻击的威力。与传统的、臭名昭著的噪声时序攻击不同,SGX-Step 可以_线性_时间确定性逐字符暴力破解密码:

## 概述

与之前的飞地抢占提案相比,SGX-Step 设计的关键在于为保存页表条目的物理内存位置、本地 APIC 内存映射 I/O 配置寄存器以及 x86 中断描述符表(IDT)创建用户空间虚拟内存映射。这允许一个不受信任的、攻击者控制的主机进程轻松地 (i) 跟踪或修改飞地页表条目,(ii) 配置 APIC 定时器单次/周期性中断源,(iii) 触发处理器间中断,以及 (iv) 完全在_用户空间_注册自定义中断处理程序。

上图总结了我们通过框架中断和恢复 SGX 飞地的硬件和软件步骤序列。

1. 本地 APIC 定时器中断在飞地指令内到达。

2. 处理器执行 AEX procedure,将执行上下文安全存储在飞地的 SSA 帧中,初始化 CPU 寄存器,并跳转到 IDT 中注册的用户空间中断处理程序。

3. 此时,任何特定于攻击的间谍代码都可以轻松插入。

4. 库返回到用户空间 AEP 蹦床。我们修改了官方 SGX SDK 的不受信任运行时,以允许轻松注册自定义 AEP 存根。此外,为了在攻击者控制的基准调试飞地上精确评估我们的方法,SGX-Step 可以_可选地_被检测以从被中断飞地的 SSA 帧中检索存储的指令指针(使用 Linux 的 `/proc/self/mem` 接口和 `EDBGRD` 指令)。

5. 之后,我们在执行 (6) `ERESUME` 之前,通过写入初始计数内存映射 I/O 寄存器来为下一次中断配置本地 APIC 定时器。

## 源代码概述

本仓库组织如下:

```

.

├── app -- Collection of sample client applications using SGX-Step to

│ attack different victim enclave scenarios.

├── doc -- Papers and reference material.

├── kernel -- Minimal dynamically loadable Linux kernel driver to export

│ physical memory to user space and bootstrap `libsgxstep`.

├── libsgxstep -- Small user-space operating system library that implements the

│ actual SGX-Step functionality, including x86 page-table and

│ APIC timer manipulations.

└── sdk -- Bindings to use SGX-Step with different SGX SDKs and libOSs.

```

## 框架功能和应用

SGX-Step 是一个通用执行控制框架,能够以_任意_攻击者代码精确地交错受害飞地指令。SGX-Step 框架的一些主要用例总结在下图中(另请参阅本文档[底部](#bottom)的使用 SGX-Step 的出版物最新列表)。

## 构建和运行

### 0. 系统要求

SGX-Step 需要支持 [SGX](https://github.com/ayeks/SGX-hardware) 的 Intel 处理器和现成的 Linux 内核。我们的原始评估是在 i7-6500U/6700 CPU 上进行的,运行 Ubuntu 18.04 和标准 Linux 4.15.0 内核。也支持更新的 Linux 内核和发行版。

我们在下面总结了 Linux [内核参数](https://www.kernel.org/doc/html/latest/admin-guide/kernel-parameters.html)。

| Linux 内核参数 | 动机 |

| ------------------------------------ | ------------------------------------------------------------------------------------------------------------------------------------------------------------------------------ |

| `nox2apic` | 可选配置本地 APIC 设备为内存映射 I/O 模式(以使用 SGX-Step 的精确单步执行功能)。如果设置此参数,请确保在 libsgxstep/config.h 中将 X2APIC 设置为 0。或者,您可以让 CPU 保持在 x2APIC 模式,最近的 SGX-Step 发行版也应该兼容。 |

| `iomem=relaxed no_timer_check` | 抑制内核日志中不需要的警告消息。 |

| `nmi_watchdog=0` | 抑制内核 NMI 看门狗。 |

| `isolcpus=1` | 将受害进程绑定到隔离的 CPU 核心。 |

| `clearcpuid=308,295,514` | 禁用监督模式访问预防(SMAP,位 295)、监督模式执行预防(SMEP,位 308)和用户模式指令预防(UMIP,位 514)功能。 |

| `pti=off` | 禁用内核页表隔离(以避免用户 IRQ 处理程序导致内核崩溃)。 |

| `rcupdate.rcu_cpu_stall_suppress=1` | 禁用内核的读-复制更新(RCU)CPU 停滞检测器(以避免长时间单步执行而不调用内核定时器中断处理程序时产生警告。) |

| `msr.allow_writes=on` | 抑制 SGX-Step 对模型特定寄存器(MSR)写入的内核警告消息。 |

| `vdso=0` | 仅在最近的 Linux 内核上:禁用 vdso_sgx_enter_enclave 库(与 AEP 拦截补丁不兼容)。 |

| `dis_ucode_ldr` | 可选禁用 CPU 微码更新(最近的瞬态执行攻击缓解可能需要重新校准单步执行间隔)。 |

按如下方式将所需的启动参数传递给内核:

```

# if you don't have vim, use nano instead

$ sudo vim /etc/default/grub

# Add the following line: GRUB_CMDLINE_LINUX_DEFAULT="quiet splash iomem=relaxed no_timer_check clearcpuid=308,295,514 pti=off isolcpus=1 nmi_watchdog=0 rcupdate.rcu_cpu_stall_suppress=1 msr.allow_writes=on vdso=0"

$ sudo update-grub && reboot

```

要检查当前运行的内核配置是否正确,请执行:

```

$ sudo ./check_sys.sh

.. Checking recommended SGX-Step parameters [OK]

.. Checking unknown kernel parameters [OK]

.. Checking CPU features [OK]

.. Checking kernel page-table isolation [OK]

```

最后,为了提高整体执行时间稳定性,您可以选择在 BIOS 配置中禁用 C-States 和 SpeedStep 技术。

### 1. 构建和加载 `/dev/sgx-step`

SGX-Step 带有一个可加载内核模块,向 `libsgxstep` 用户空间库导出 IOCTL 接口。驱动程序主要负责 (i) 挂钩 APIC 定时器中断处理程序,(ii) 收集不受信任的页表映射,以及 (iii) 可选地获取被中断的基准飞地的指令指针。

要构建和加载 `/dev/sgx-step` 驱动程序,请执行:

```

$ cd kernel/

$ ./install_SGX_driver.sh # tested on Ubuntu 20.04/22.04

$ make clean load

```

**注意(/dev/sgx_enclave)。** SGX-Step 支持传统 Intel `/dev/isgx` 树外驱动程序(应该适用于所有平台),以及适用于具有最新 Linux 内核 >5.11 且支持灵活启动控制的平台的树内 `/dev/sgx_enclave` 驱动程序。`install_SGX_driver.sh` 脚本应自动检测树内 `/dev/sgx-enclave` 驱动程序是否可用,如果不可用,则通过指向未修改的 v2.14 [linux-sgx-driver](_URL_9/>) 的 git 子模块构建和加载树外 `/dev/isgx` 驱动程序。

**注意(/dev/mem)。** 我们依赖 Linux 的虚拟 `/dev/mem` 设备来构建 APIC 物理内存映射 I/O 寄存器和感兴趣页表条目的用户级虚拟内存映射。然而,最近的 Linux 发行版通常启用 `CONFIG_STRICT_DEVMEM` 选项来阻止这种使用。因此,我们的 `/dev/sgx-step` 驱动程序包含一种[方法](https://www.libcrack.so/index.php/2012/09/02/bypassing-devmem_is_allowed-with-kprobes/)来绕过 `devmem_is_allowed` 检查,而无需重新编译内核。

### 2. 补丁和安装 SGX SDK

为了轻松注册自定义异步退出指针(AEP)存根,我们修改了官方 Intel SGX SDK 的不受信任运行时。按以下步骤检出 [linux-sgx](https://github.com/01org/linux-sgx) v2.23 并应用我们的补丁。

```

$ cd sdk/intel-sdk/

$ ./install_SGX_SDK.sh # tested on Ubuntu 20.04/22.04

$ source /opt/intel/sgxsdk/environment # add to ~/.bashrc to preserve across terminal sessions

$ sudo service aesmd status # stop/start aesmd service if needed

```

上述安装脚本已在 Ubuntu 22.04 LTS 上测试。

对于其他 GNU/Linux 发行版,请按照 [linux-sgx](https://github.com/01org/linux-sgx) 项目中的说明构建和安装 Intel SGX SDK 和 PSW 包。您还需要构建和加载一个(未修改的)[linux-sgx-driver](https://github.com/01org/linux-sgx-driver) SGX 内核模块才能使用 SGX-Step。

**注意(本地安装)。** 补丁 SGX SDK 和 PSW 包可以本地安装,而不会影响兼容的系统级 'linux-sgx' 安装。为此,示例 Makefile 支持指向本地 SDK 安装目录的 `SGX_SDK` 环境变量。当检测到非默认 SDK 路径(即不是 `/opt/intel/sgxsdk`)时,"run" Makefile 目标还会动态链接到本地 `linux-sgx` 目录中构建的补丁 `libsgx_urts.so` 不受信任运行时(使用 `LD_LIBRARY_PATH` 环境变量)。

**注意(32 位支持)。** 构建 32 位版本 SGX SDK 和 SGX-Step 的说明(已过时且未维护!)可在 [README-m32.md](README-m32.md) 中找到。

### 3. 构建和运行测试应用程序

用户空间应用程序可以链接到 `libsgxstep` 库以使用 SGX-Step 的单步执行和页表操作功能。请查看 "app" 目录中的示例应用程序。

首先,检查 APIC 和中断描述符表设置:

```

$ cd app/selftest/idt

$ make run # fires interrupts in an infinite loop to stress-test stability; exit with CTRL-C

```

例如,要构建和运行一个测试页表操作功能和 SDK 补丁的基本示例应用程序:

```

$ cd app/aep-redirect

$ make run

```

要测试定时器单步执行功能,可以尝试构建和运行一个基准飞地来单步执行 100 个连续的 `nop` 指令:

```

$ cd app/bench

$ NUM=100 make parse # alternatively vary NUM and use STRLEN=1 or ZIGZAG=1

```

上述命令构建 `libsgxstep`、基准受害飞地和不受信任的攻击者主机进程,其中攻击场景和实例大小通过相应的环境变量配置。该命令还非交互式运行生成的二进制文件(以确保确定性定时器间隔),最后调用特定于攻击的后处理 Python 脚本来解析生成的飞地指令指针基准结果。

**注意(性能)。** 单步执行飞地执行会产生相当大的减速。我们测量到论文中描述的实验执行时间长达 15 分钟。SGX-Step 的页表操作功能允许仅对选定函数启动单步执行,例如通过撤销特定感兴趣代码或数据页的访问权限。

**注意(定时器间隔)。** 确切的定时器间隔值取决于 CPU 频率,因此本质上仍然是平台特定的(另请参阅 [app/selftest/apic](app/selftest/apic) 了解评估各种 APIC 定时器模式准确性的详细微基准测试)。在 `/app/bench/main.c` 中配置合适的值。我们通过调整和观察 NOP 微基准测试飞地指令指针跟踪结果,为我们的评估平台确定了精确的定时器间隔(见下表),如下所述。

**注意(稳定性)。** 为了避免 Linux 内核卡住或崩溃,SGX-Step 应在退出 `libsgxstep` 进程后自动恢复中断描述符表和本地 APIC 定时器。您可以按如下方式检查 APIC 定时器是否仍在所有核心上触发:

```

$ watch -n0.1 "cat /proc/interrupts | grep 'Local timer interrupts'"

```

## 校准单步执行间隔

下表列出了当前支持的 Intel CPU 及其单步执行 APIC 定时器间隔(`libsgxstep/config.h`)。

请注意,确切的单步执行间隔可能取决于处理器的微码版本,当最近的[瞬态执行攻击](https://transient.fail/) 缓解措施在飞地进入/退出时刷新微架构缓冲区时更是如此。下表中提供了一些不同的微码版本作为参考。

| 型号名称 | CPU | 基础频率 | 微码(日期) | APIC 定时器间隔 |

| ------------- | --------------------------------------------------------------------------------------------------------------------------------------- | -------------- | ----------------------- | ------------------- |

| Skylake | [i7-6700](https://ark.intel.com/products/88196) | 3.4 GHz | ? | 19 |

| Skylake | [i7-6500U](https://ark.intel.com/products/88194) | 2.5 GHz | ? | 25 |

| Skylake | [i5-6200U](https://ark.intel.com/products/88193) | 2.3 GHz | ? | 28 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | ? | 34 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | 0xca (2019-10-03) | 54 |

| Coffee Lake R | [i7-9700](https://ark.intel.com/content/www/us/en/ark/products/191792/intel-core-i79700-processor-12m-cache-up-to-4-70-ghz.html) | 3 GHz | 0xf4 (2022-07-31) | 26 |

| Coffee Lake R | [i9-9900K](https://ark.intel.com/products/186605) | 3.6 GHz | ? | 21 |

| Coffee Lake HR | [i7-9750H](https://ark.intel.com/content/www/us/en/ark/products/191045/intel-core-i7-9750h-processor-12m-cache-up-to-4-50-ghz.html) | 2.6 GHz | 0xf4 (2023-02-23) | 37 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0x32 (2019-07-05) | 135 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0xb0 (2022-03-09) | 255 |

| Comet Lake | [i9-10900K](https://www.intel.com/content/www/us/en/products/sku/199332/intel-core-i910900k-processor-20m-cache-up-to-5-30-ghz.html) | 3.70 GHz | 0xfc (2024-02-01) | 24 |

| Emerald Rapids | [Xeon Gold 5515+](https://ark.intel.com/content/www/us/en/ark/products/237562/intel-xeon-gold-5515-processor-22-5m-cache-3-20-ghz.html) | 3.2 GHz | 0x21000230 (2024-02-05) | 32 |

**注意(校准)。**

目前,配置可靠定时器间隔的最简单方法是使用 `app/bench` 基准测试工具和长 NOP 滑动,并逐渐增加/减少 `SGX_STEP_TIMER_INTERVAL`。您可以从大约 20 开始,然后执行 `NUM=100 make parse` 来获取 100 条指令 NOP 滑动的单步、零步和多步摘要(一旦您有了更稳定的间隔,您可以切换到更长的滑动)。零步太多表明您需要增加定时器间隔,而多步则需要降低定时器间隔。

**注意(过滤零步)。**

重要提示:当剩下一些零步时不要担心,只要您取得进展,您可以通过查看飞地的代码 PTE 访问位(该位仅在指令实际退休并发生单步时设置)来确定性地过滤掉零步。因此,在配置了保守的定时器间隔以始终避免多步之后,SGX-Step 可以实现_完美的_指令级粒度的无噪声单步执行。

**注意(扩展中断"着陆窗口")。**

如下面的根本原因分析所阐明的,解析 `ERESUME` 后第一个飞地指令(代码)地址的页表遍历越慢,中断"着陆窗口"就越长,因此 SGX-Step 的单步执行可靠性就越高。例如,我们发现,除了清除飞地的 PMD 访问位之外,通过在 `ERESUME` 之前从 CPU 缓存刷新一个或多个不受保护的页表条目,可以进一步扩展着陆窗口,迫使 CPU 在页表遍历期间等待慢速内存。因此,当您找不到可靠的定时器间隔配置时,请确保 (i) 清除飞地的代码 PTE/PMD "访问"位,(ii) 在 AEP 处理程序中刷新(`CLFLUSH`)一个或多个飞地页表条目。

**注意(微码)。**

另一个警告涉及最近的 Foreshadow/ZombieLoad/RIDL/etc 微码缓解措施,这些措施在飞地进入/退出时刷新易受攻击的 uarch 缓冲区。请注意,当启用这些缓解措施时,定时器间隔将需要增加,因为飞地进入需要更长时间(例如,在我 的 i7-8650U CPU 上,我发现单步定时器间隔上升到 54,而使用 Foreshadow 之前的微码仅为 34)。

额外的刷新操作可能还会增加飞地进入时间的方差,这意味着您可能需要更保守地配置定时器,并允许更多零步(可以如上所述确定性地过滤掉)。

### SGX-Step 根本原因分析

关于 SGX-Step 如何可靠地中断臭名昭著复杂的 `ERESUME` 指令之后的第一个(可能非常短的!)飞地指令的详细根本原因分析在 [AEX-Notify](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) 论文中有描述。

我们发现 SGX-Step 成功的关键在于使用"访问"(A) 位。具体来说,SGX-Step 在配置 APIC 触发单次中断之前,始终清除受害飞地页中间目录(PMD)中的 A 位。A 位仅在飞地至少执行一条指令时才会被处理器设置,因此可用于确定性地区分零步和单步。

关键的是,由于处理器的页未命中处理程序针对常见的快速路径进行了优化,并使用慢得多的"微码辅助"来处理不太频繁且更复杂的需要修改 PMD 或 PTE 的情况,这种辅助的效果是将 `ERSUME` 后的第一个飞地指令的执行延长数百个周期。因此,这个"辅助窗口"为粗粒度的、通常分布式的 APIC 定时器中断提供了宽敞的着陆空间,使其能够高精度到达。

## 在您自己的项目中使用 SGX-Step

在您自己的项目中开始使用 SGX-Step 框架的最简单方法是通过 [git 子模块](https://git-scm.com/book/en/v2/Git-Tools-Submodules):

```

$ cd my/git/project

$ git submodule add https://github.com/jovanbulck/sgx-step.git

$ cd sgx-step # Now build `/dev/sgx-step` and `libsgxstep` as described above

```

请查看 `app` 目录中的 Makefile,了解客户端应用程序如何链接到 `libsgxstep` 以及任何本地 SGX SDK/PSW 包。

以下是使用 SGX-Step 的已知项目列表。如果您的项目使用了 SGX-Step 但未包含在下面,请随时提交拉取请求。

| 标题 | 出版物详情 | 源代码 | 使用的 SGX-Step 功能 |

| ---------------------------------------------------------------------------------------------- | -------------------------------------------------------------------------------------------- | ------------------------------------------------------------------------- | ------------------------------------------------------- |

| AEX-NStep: Probabilistic Interrupt Counting Attacks on Intel SGX | [S&P'26](https://arxiv.org/pdf/2510.14675) | [Zenodo](https://zenodo.org/records/17338383) | Page faults, IPIs, WRMSR Interrupt Gate |

| MDPeek: Breaking Balanced Branches in SGX with Memory Disambiguation Unit Side Channels | [ASPLOS'25](https://www.comp.nus.edu.sg/~tcarlson/pdfs/liu2025mbbbiswmdusc.pdf) | [GitHub (Artifact Evaluated & Functional)](https://github.com/CPU-THU/MDPeek) | Page faults |

| Activation Functions Considered Harmful: Recovering Neural Network Weights through Controlled Channels | [ArXiv'25](https://arxiv.org/pdf/2503.19142) | - | Single-stepping, PTE A/D |

| TLBlur: Compiler-Assisted Automated Hardening against Controlled Channels on Off-the-Shelf Intel SGX Platforms | [USEC'25](https://vanbulck.net/files/usenix25-tlblur.pdf) | [GitHub (full)](https://github.com/TLBlur-SGX) | Single-stepping, PTE A/D, page faults |

| POSTER: On the Feasibility of Inferring SGX Execution through PMU | [AsiaCCS'24](https://dl.acm.org/doi/pdf/10.1145/3634737.3659434) | - | Single-stepping, zero-stepping|

| SIGY: Breaking Intel SGX Enclaves with Malicious Exceptions & Signals | [ArXiv'24](https://arxiv.org/abs/2404.13998) | - | Timer interrupts, page faults |

| On (the Lackin) Code Confidentiality in Trusted Execution Environments | [S&P24](https://ivanpuddu.com/files/papers/TEE_WASM_code_Leakage.pdf) | [GitHub (empty)](https://github.com/dn0sar/TEE-WASM-Code-Extraction) | Single-stepping |

| TeeJam: Sub-Cache-Line Leakages Strike Back | [CHES24](https://doi.org/10.46586/tches.v2024.i1.457-500) | [Github (full)](https://github.com/UzL-ITS/teejam) | Single-stepping interrupt latency, PTE A/D |

| AEX-Notify: Thwarting Precise Single-Stepping Attacks through Interrupt Awareness for Intel SGX Enclaves | [USEC23](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) | [GitHub (SGX SDK mitigation)](https://github.com/intel/linux-sgx/blob/master/sdk/trts/linux/trts_mitigation.S) | Single-Stepping, PTE A/D

| Controlled Data Races in Enclaves: Attacks and Detection | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-chen-sanchuan.pdf) | [GitHub (non-attack)](https://github.com/OSUSecLab/SGXRacer) | Single-stepping, APIC |

| BunnyHop: Exploiting the Instruction Prefetcher | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-zhang-zhiyuan-bunnyhop.pdf) | [GitHub (non-SGX PoC)](https://github.com/0xADE1A1DE/BunnyHop) | Single-stepping, PTE A/D |

| Downfall: Exploiting Speculative Data Gathering | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-moghimi.pdf) | [GitHub (non-SGX PoC)](https://github.com/flowyroll/downfall/tree/main/POC) | Single-stepping, zero-stepping |

| All Your PC Are Belong to Us: Exploiting Non-control-Transfer Instruction BTB Updates for Dynamic PC Extraction | [ISCA23](https://dl.acm.org/doi/pdf/10.1145/3579371.3589100?casa_token=Q5jf5nOgiLIAAAAA:cT0ltJh7vk943buODuR4oMFKmuhg2Tp-djFm2kUu6DzlxtBhNhEw2WteRggn0k99D7ft-P6pluVrFA) | - | Single-stepping |

| Cache-timing attack against HQC | [CHES23](https://eprint.iacr.org/2023/102.pdf) | - | Single-stepping, PTE A/D |

| FaultMorse: An automated controlled-channel attack via longest recurring sequence | [ComSec23](https://www.sciencedirect.com/science/article/pii/S0167404822003959) | [GitHub (post processing)](https://github.com/Ezekiel-1998/FaultMorse) | Page fault |

| AEPIC Leak: Architecturally Leaking Uninitialized Data from the Microarchitecture | [USEC22](https://www.usenix.org/system/files/sec22-borrello.pdf) | [GitHub (full)](https://github.com/IAIK/AEPIC) | Single-Stepping, PTE A/D |

| MoLE: Mitigation of Side-channel Attacks against SGX via Dynamic Data Location Escape | [ACSAC22](https://dl.acm.org/doi/fullHtml/10.1145/3564625.3568002) | - | Single-Stepping, page fault, transient execution |

| WIP: Interrupt Attack on TEE-Protected Robotic Vehicles | [AutoSec22](https://www.ndss-symposium.org/wp-content/uploads/autosec2022_23001_paper.pdf) | - | Single-stepping, multi-stepping |

| Towards Self-monitoring Enclaves: Side-Channel Detection Using Performance Counters | [NordSec22](https://link.springer.com/chapter/10.1007/978-3-031-22295-5_7) | - | Page fault, LVI. |

| ENCLYZER: Automated Analysis of Transient Data Leaks on Intel SGX | [SEED22](https://ieeexplore.ieee.org/document/9935016) | [GitHub (full)](https://github.com/bloaryth/enclyser) | Page-table manipulation |

| Side-Channeling the Kalyna Key Expansion | [CT-RSA22](https://cs.adelaide.edu.au/~yval/pdfs/ChuengsatiansupGYZ22.pdf) | - | Single-Stepping, PTE A/D |

| Rapid Prototyping for Microarchitectural Attacks | [USENIX22](https://www.usenix.org/system/files/sec22summer_easdon.pdf) | [GitHub (full)](https://github.com/libtea/frameworks) | Single-stepping, page fault, PTE A/D, etc. |

| Util::Lookup: Exploiting Key Decoding in Cryptographic Libraries | [CCS21](https://dl.acm.org/doi/abs/10.1145/3460120.3484783) | [GitHub (full)](https://github.com/UzL-ITS/util-lookup) | Single-Stepping, PTE A/D |

| SmashEx: Smashing SGX Enclaves Using Exceptions | [CCS21](https://dl.acm.org/doi/pdf/10.1145/3460120.3484821) | - | Single-stepping |

| Online Template Attacks: Revisited | [CHES21](https://tches.iacr.org/index.php/TCHES/article/view/8967/8545) | [Zenodo (simulation)](https://zenodo.org/record/4680071) | Single-stepping, page fault, PTE A/D |

| Aion Attacks: Manipulating Software Timers in Trusted Execution | [DIMVA21](http://individual.utoronto.ca/shengjiexu/publication/whuang-dimva2021-aion_v2.pdf) | - | Single-stepping, interrupts(?) |

| Platypus: Software-based Power Side-Channel Attacks on x86 | [S&P21](https://platypusattack.com/platypus.pdf) | [GitHub (simulated PoC)](https://github.com/0xhilbert/Platypus) | Single-stepping, zero-stepping |

| CrossTalk: Speculative Data Leaks Across Cores Are Real | [S&P21](https://download.vusec.net/papers/crosstalk_sp21.pdf) | - | Single-stepping, page fault |

| Frontal Attack: Leaking Control-Flow in SGX via the CPU Frontend | [USEC21](https://www.usenix.org/system/files/sec21-puddu.pdf) | [GitHub (full, artifact evaluated)](https://github.com/dn0sar/frontal_poc) | Single-stepping interrupt latency, PTE A/D |

| PThammer: Cross-User-Kernel-Boundary Rowhammer through Implicit Accesses | - | [MICRO20](https://arxiv.org/pdf/2007.08707v2.pdf) | Page table walk |

| SpeechMiner: A Framework for Investigating andMeasuring Speculative Execution Vulnerabilities | [NDSS20](https://www.ndss-symposium.org/wp-content/uploads/2020/02/23105-paper.pdf) | [GitHub (full)](https://github.com/teecert/SpeechMiner) | Page-table manipulation |

| Déjà Vu: Side-Channel Analysis of Mozilla's NSS | [CCS20](https://dl.acm.org/doi/pdf/10.1145/3372297.3421761) | - | Page fault |

| From A to Z: Projective coordinates leakage in the wild | [CHES20](https://eprint.iacr.org/2020/432.pdf) | - | Page fault |

| LVI: Hijacking Transient Execution through Microarchitectural Load Value Injection | [S&P20](https://lviattack.eu/lvi.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step-lvi/tree/master/app/lvi) | Single-stepping, page-table manipulation |

| CopyCat: Controlled Instruction-Level Attacks on Enclaves | [USEC20](https://arxiv.org/pdf/2002.08437.pdf) | - | Single-stepping, page fault, PTE A/D |

| When one vulnerable primitive turns viral: Novel single-trace attacks on ECDSA and RSA | [CHES20](https://eprint.iacr.org/2020/055.pdf) | - | Single-stepping, page fault, PTE A/D |

| Big numbers - Big Troubles: Systematically Analyzing Nonce Leakage in (EC)DSA Implementations | [USEC20](https://www.usenix.org/system/files/sec20summer_weiser_prepub_0.pdf) | - | Page fault |

| Plundervolt: Software-based Fault Injection Attacks against Intel SGX | [S&P20](https://plundervolt.com/doc/plundervolt.pdf) | [GitHub (full)](https://github.com/KitMurdock/plundervolt) | Privileged interrupt/call gates, MSR |

| Bluethunder: A 2-level Directional Predictor Based Side-Channel Attack against SGX | [CHES20](https://heartever.github.io/files/bluethunder_sgx_ches.pdf) | - | Single-stepping |

| Fallout: Leaking Data on Meltdown-resistant CPUs | [CCS19](https://mdsattacks.com/files/fallout.pdf) | - | PTE A/D |

| A Tale of Two Worlds: Assessing the Vulnerability of Enclave Shielding Runtimes | [CCS19](https://people.cs.kuleuven.be/~jo.vanbulck/ccs19-tale.pdf) | [GitHub (full)](https://github.com/jovanbulck/0xbadc0de) | Single-stepping, page fault, PTE A/D |

| ZombieLoad: Cross-Privilege-Boundary Data Sampling | [CCS19](https://zombieloadattack.com/zombieload.pdf) | [GitHub (PoC)](https://github.com/IAIK/ZombieLoad/) | Single-stepping, zero-stepping, page-table manipulation |

| SPOILER: Speculative Load Hazards Boost Rowhammer and Cache Attacks | [USEC19](https://arxiv.org/pdf/1903.00446.pdf) | - | Single-stepping interrupt latency |

| Nemesis: Studying Microarchitectural Timing Leaks in Rudimentary CPU Interrupt Logic | [CCS18](https://people.cs.kuleuven.be/~jo.vanbulck/ccs18.pdf) | [GitHub (full)](https://github.com/jovanbulck/nemesis) | Single-stepping interrupt latency, page fault, PTE A/D |

| Foreshadow: Extracting the Keys to the Intel SGX Kingdom with Transient Out-of-Order Execution | [USEC18](https://foreshadowattack.eu/foreshadow.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step/tree/master/app/foreshadow) | Single-stepping, zero-stepping, page-table manipulation |

| Single Trace Attack Against RSA Key Generation in Intel SGX SSL | [AsiaCCS18](https://rspreitzer.github.io/publications/proc/asiaccs-2018-paper-1.pdf) | - | Page fault |

| Off-Limits: Abusing Legacy x86 Memory Segmentation to Spy on Enclaved Execution | [ESSoS18](https://people.cs.kuleuven.be/~jo.vanbulck/essos18.pdf) | [link (full, artifact evaluated)](https://distrinet.cs.kuleuven.be/software/off-limits/) | Single-stepping, IA32 segmentation, page fault |

| SGX-Step: A Practical Attack Framework for Precise Enclave Execution Control | [SysTEX17](https://people.cs.kuleuven.be/~jo.vanbulck/systex17.pdf) | [GitHub (full)](https://github.com/jovanbulck/sgx-step/tree/master/app/bench) | Single-stepping, page fault, PTE A/D |

SGX-Step 是一个开源框架,用于促进 Intel x86 处理器(尤其是 Intel SGX 平台)的侧信道攻击研究。

SGX-Step 由一个对抗性 Linux 内核驱动程序和一个小型用户空间操作系统库组成,允许完全从用户空间配置不受信任的页表条目和/或 x86 APIC 定时器中断。SGX-Step 已被我们的研究以及独立研究人员所利用,实现了多个新的和改进的飞地执行攻击,能够以最高的时间分辨率收集侧信道观察结果(即,在受害飞地执行_每一条_指令后进行中断)。

**许可证。** SGX-Step 是免费软件,采用 [GPLv3](https://www.gnu.org/licenses/gpl-3.0) 许可证。SGX-Step 的标志来源于 Eadweard Muybridge 著名的[公有领域](https://en.wikipedia.org/wiki/Sallie_Gardner_at_a_Gallop)"Sallie Gardner at a Gallop"照片系列,与我们的飞地单步执行目标相似,将奔跑的马动态分解为一系列单独的照片帧,以揭示整体的马步态特性。

| SGX-Step 版本 | 变更日志功能 |

| -------------- | ------------------------------------------------------------------------------ |

| v1.5.0 | 稳定化修复(KPTI,内核 ISR 映射);(实验性)Gramine 移植;IPI 支持。 |

| v1.4.0 | 特权中断/调用门(Plundervolt)。 |

| v1.3.0 | 瞬态执行支持(Foreshadow)。 |

| v1.2.0 | 用户空间中断处理和确定性零步过滤(Nemesis)。 |

| v1.1.0 | IA32 支持。 |

| v1.0.0 | 用户空间页表操作和 APIC 定时器单步执行。 |

**出版物。** SGX-Step 已被多个独立研究小组采用,并开创了一系列高分辨率 SGX 攻击。使用 SGX-Step 的已知项目完整最新列表包含在本文档[底部](#bottom)。原始论文的副本可在[此处](https://jovanbulck.github.io/files/systex17-sgxstep.pdf)获取。

```

@inproceedings{vanbulck2017sgxstep,

title = {{SGX-Step}: A Practical Attack Framework for Precise Enclave Execution Control},

author = {Van Bulck, Jo and Piessens, Frank and Strackx, Raoul},

booktitle = {2nd Workshop on System Software for Trusted Execution {(SysTEX)}},

publisher = {{ACM}},

pages = {4:1--4:6},

month = Oct,

year = 2017,

}

```

**演示。** [app/memcmp](app/memcmp) 目录包含一个演示应用程序,通过单步执行一个包含微妙、非恒定时间 `memcmp` 密码比较逻辑的示例飞地来说明 SGX-Step 攻击的威力。与传统的、臭名昭著的噪声时序攻击不同,SGX-Step 可以_线性_时间确定性逐字符暴力破解密码:

## 概述

与之前的飞地抢占提案相比,SGX-Step 设计的关键在于为保存页表条目的物理内存位置、本地 APIC 内存映射 I/O 配置寄存器以及 x86 中断描述符表(IDT)创建用户空间虚拟内存映射。这允许一个不受信任的、攻击者控制的主机进程轻松地 (i) 跟踪或修改飞地页表条目,(ii) 配置 APIC 定时器单次/周期性中断源,(iii) 触发处理器间中断,以及 (iv) 完全在_用户空间_注册自定义中断处理程序。

上图总结了我们通过框架中断和恢复 SGX 飞地的硬件和软件步骤序列。

1. 本地 APIC 定时器中断在飞地指令内到达。

2. 处理器执行 AEX procedure,将执行上下文安全存储在飞地的 SSA 帧中,初始化 CPU 寄存器,并跳转到 IDT 中注册的用户空间中断处理程序。

3. 此时,任何特定于攻击的间谍代码都可以轻松插入。

4. 库返回到用户空间 AEP 蹦床。我们修改了官方 SGX SDK 的不受信任运行时,以允许轻松注册自定义 AEP 存根。此外,为了在攻击者控制的基准调试飞地上精确评估我们的方法,SGX-Step 可以_可选地_被检测以从被中断飞地的 SSA 帧中检索存储的指令指针(使用 Linux 的 `/proc/self/mem` 接口和 `EDBGRD` 指令)。

5. 之后,我们在执行 (6) `ERESUME` 之前,通过写入初始计数内存映射 I/O 寄存器来为下一次中断配置本地 APIC 定时器。

## 源代码概述

本仓库组织如下:

```

.

├── app -- Collection of sample client applications using SGX-Step to

│ attack different victim enclave scenarios.

├── doc -- Papers and reference material.

├── kernel -- Minimal dynamically loadable Linux kernel driver to export

│ physical memory to user space and bootstrap `libsgxstep`.

├── libsgxstep -- Small user-space operating system library that implements the

│ actual SGX-Step functionality, including x86 page-table and

│ APIC timer manipulations.

└── sdk -- Bindings to use SGX-Step with different SGX SDKs and libOSs.

```

## 框架功能和应用

SGX-Step 是一个通用执行控制框架,能够以_任意_攻击者代码精确地交错受害飞地指令。SGX-Step 框架的一些主要用例总结在下图中(另请参阅本文档[底部](#bottom)的使用 SGX-Step 的出版物最新列表)。

## 构建和运行

### 0. 系统要求

SGX-Step 需要支持 [SGX](https://github.com/ayeks/SGX-hardware) 的 Intel 处理器和现成的 Linux 内核。我们的原始评估是在 i7-6500U/6700 CPU 上进行的,运行 Ubuntu 18.04 和标准 Linux 4.15.0 内核。也支持更新的 Linux 内核和发行版。

我们在下面总结了 Linux [内核参数](https://www.kernel.org/doc/html/latest/admin-guide/kernel-parameters.html)。

| Linux 内核参数 | 动机 |

| ------------------------------------ | ------------------------------------------------------------------------------------------------------------------------------------------------------------------------------ |

| `nox2apic` | 可选配置本地 APIC 设备为内存映射 I/O 模式(以使用 SGX-Step 的精确单步执行功能)。如果设置此参数,请确保在 libsgxstep/config.h 中将 X2APIC 设置为 0。或者,您可以让 CPU 保持在 x2APIC 模式,最近的 SGX-Step 发行版也应该兼容。 |

| `iomem=relaxed no_timer_check` | 抑制内核日志中不需要的警告消息。 |

| `nmi_watchdog=0` | 抑制内核 NMI 看门狗。 |

| `isolcpus=1` | 将受害进程绑定到隔离的 CPU 核心。 |

| `clearcpuid=308,295,514` | 禁用监督模式访问预防(SMAP,位 295)、监督模式执行预防(SMEP,位 308)和用户模式指令预防(UMIP,位 514)功能。 |

| `pti=off` | 禁用内核页表隔离(以避免用户 IRQ 处理程序导致内核崩溃)。 |

| `rcupdate.rcu_cpu_stall_suppress=1` | 禁用内核的读-复制更新(RCU)CPU 停滞检测器(以避免长时间单步执行而不调用内核定时器中断处理程序时产生警告。) |

| `msr.allow_writes=on` | 抑制 SGX-Step 对模型特定寄存器(MSR)写入的内核警告消息。 |

| `vdso=0` | 仅在最近的 Linux 内核上:禁用 vdso_sgx_enter_enclave 库(与 AEP 拦截补丁不兼容)。 |

| `dis_ucode_ldr` | 可选禁用 CPU 微码更新(最近的瞬态执行攻击缓解可能需要重新校准单步执行间隔)。 |

按如下方式将所需的启动参数传递给内核:

```

# if you don't have vim, use nano instead

$ sudo vim /etc/default/grub

# Add the following line: GRUB_CMDLINE_LINUX_DEFAULT="quiet splash iomem=relaxed no_timer_check clearcpuid=308,295,514 pti=off isolcpus=1 nmi_watchdog=0 rcupdate.rcu_cpu_stall_suppress=1 msr.allow_writes=on vdso=0"

$ sudo update-grub && reboot

```

要检查当前运行的内核配置是否正确,请执行:

```

$ sudo ./check_sys.sh

.. Checking recommended SGX-Step parameters [OK]

.. Checking unknown kernel parameters [OK]

.. Checking CPU features [OK]

.. Checking kernel page-table isolation [OK]

```

最后,为了提高整体执行时间稳定性,您可以选择在 BIOS 配置中禁用 C-States 和 SpeedStep 技术。

### 1. 构建和加载 `/dev/sgx-step`

SGX-Step 带有一个可加载内核模块,向 `libsgxstep` 用户空间库导出 IOCTL 接口。驱动程序主要负责 (i) 挂钩 APIC 定时器中断处理程序,(ii) 收集不受信任的页表映射,以及 (iii) 可选地获取被中断的基准飞地的指令指针。

要构建和加载 `/dev/sgx-step` 驱动程序,请执行:

```

$ cd kernel/

$ ./install_SGX_driver.sh # tested on Ubuntu 20.04/22.04

$ make clean load

```

**注意(/dev/sgx_enclave)。** SGX-Step 支持传统 Intel `/dev/isgx` 树外驱动程序(应该适用于所有平台),以及适用于具有最新 Linux 内核 >5.11 且支持灵活启动控制的平台的树内 `/dev/sgx_enclave` 驱动程序。`install_SGX_driver.sh` 脚本应自动检测树内 `/dev/sgx-enclave` 驱动程序是否可用,如果不可用,则通过指向未修改的 v2.14 [linux-sgx-driver](_URL_9/>) 的 git 子模块构建和加载树外 `/dev/isgx` 驱动程序。

**注意(/dev/mem)。** 我们依赖 Linux 的虚拟 `/dev/mem` 设备来构建 APIC 物理内存映射 I/O 寄存器和感兴趣页表条目的用户级虚拟内存映射。然而,最近的 Linux 发行版通常启用 `CONFIG_STRICT_DEVMEM` 选项来阻止这种使用。因此,我们的 `/dev/sgx-step` 驱动程序包含一种[方法](https://www.libcrack.so/index.php/2012/09/02/bypassing-devmem_is_allowed-with-kprobes/)来绕过 `devmem_is_allowed` 检查,而无需重新编译内核。

### 2. 补丁和安装 SGX SDK

为了轻松注册自定义异步退出指针(AEP)存根,我们修改了官方 Intel SGX SDK 的不受信任运行时。按以下步骤检出 [linux-sgx](https://github.com/01org/linux-sgx) v2.23 并应用我们的补丁。

```

$ cd sdk/intel-sdk/

$ ./install_SGX_SDK.sh # tested on Ubuntu 20.04/22.04

$ source /opt/intel/sgxsdk/environment # add to ~/.bashrc to preserve across terminal sessions

$ sudo service aesmd status # stop/start aesmd service if needed

```

上述安装脚本已在 Ubuntu 22.04 LTS 上测试。

对于其他 GNU/Linux 发行版,请按照 [linux-sgx](https://github.com/01org/linux-sgx) 项目中的说明构建和安装 Intel SGX SDK 和 PSW 包。您还需要构建和加载一个(未修改的)[linux-sgx-driver](https://github.com/01org/linux-sgx-driver) SGX 内核模块才能使用 SGX-Step。

**注意(本地安装)。** 补丁 SGX SDK 和 PSW 包可以本地安装,而不会影响兼容的系统级 'linux-sgx' 安装。为此,示例 Makefile 支持指向本地 SDK 安装目录的 `SGX_SDK` 环境变量。当检测到非默认 SDK 路径(即不是 `/opt/intel/sgxsdk`)时,"run" Makefile 目标还会动态链接到本地 `linux-sgx` 目录中构建的补丁 `libsgx_urts.so` 不受信任运行时(使用 `LD_LIBRARY_PATH` 环境变量)。

**注意(32 位支持)。** 构建 32 位版本 SGX SDK 和 SGX-Step 的说明(已过时且未维护!)可在 [README-m32.md](README-m32.md) 中找到。

### 3. 构建和运行测试应用程序

用户空间应用程序可以链接到 `libsgxstep` 库以使用 SGX-Step 的单步执行和页表操作功能。请查看 "app" 目录中的示例应用程序。

首先,检查 APIC 和中断描述符表设置:

```

$ cd app/selftest/idt

$ make run # fires interrupts in an infinite loop to stress-test stability; exit with CTRL-C

```

例如,要构建和运行一个测试页表操作功能和 SDK 补丁的基本示例应用程序:

```

$ cd app/aep-redirect

$ make run

```

要测试定时器单步执行功能,可以尝试构建和运行一个基准飞地来单步执行 100 个连续的 `nop` 指令:

```

$ cd app/bench

$ NUM=100 make parse # alternatively vary NUM and use STRLEN=1 or ZIGZAG=1

```

上述命令构建 `libsgxstep`、基准受害飞地和不受信任的攻击者主机进程,其中攻击场景和实例大小通过相应的环境变量配置。该命令还非交互式运行生成的二进制文件(以确保确定性定时器间隔),最后调用特定于攻击的后处理 Python 脚本来解析生成的飞地指令指针基准结果。

**注意(性能)。** 单步执行飞地执行会产生相当大的减速。我们测量到论文中描述的实验执行时间长达 15 分钟。SGX-Step 的页表操作功能允许仅对选定函数启动单步执行,例如通过撤销特定感兴趣代码或数据页的访问权限。

**注意(定时器间隔)。** 确切的定时器间隔值取决于 CPU 频率,因此本质上仍然是平台特定的(另请参阅 [app/selftest/apic](app/selftest/apic) 了解评估各种 APIC 定时器模式准确性的详细微基准测试)。在 `/app/bench/main.c` 中配置合适的值。我们通过调整和观察 NOP 微基准测试飞地指令指针跟踪结果,为我们的评估平台确定了精确的定时器间隔(见下表),如下所述。

**注意(稳定性)。** 为了避免 Linux 内核卡住或崩溃,SGX-Step 应在退出 `libsgxstep` 进程后自动恢复中断描述符表和本地 APIC 定时器。您可以按如下方式检查 APIC 定时器是否仍在所有核心上触发:

```

$ watch -n0.1 "cat /proc/interrupts | grep 'Local timer interrupts'"

```

## 校准单步执行间隔

下表列出了当前支持的 Intel CPU 及其单步执行 APIC 定时器间隔(`libsgxstep/config.h`)。

请注意,确切的单步执行间隔可能取决于处理器的微码版本,当最近的[瞬态执行攻击](https://transient.fail/) 缓解措施在飞地进入/退出时刷新微架构缓冲区时更是如此。下表中提供了一些不同的微码版本作为参考。

| 型号名称 | CPU | 基础频率 | 微码(日期) | APIC 定时器间隔 |

| ------------- | --------------------------------------------------------------------------------------------------------------------------------------- | -------------- | ----------------------- | ------------------- |

| Skylake | [i7-6700](https://ark.intel.com/products/88196) | 3.4 GHz | ? | 19 |

| Skylake | [i7-6500U](https://ark.intel.com/products/88194) | 2.5 GHz | ? | 25 |

| Skylake | [i5-6200U](https://ark.intel.com/products/88193) | 2.3 GHz | ? | 28 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | ? | 34 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | 0xca (2019-10-03) | 54 |

| Coffee Lake R | [i7-9700](https://ark.intel.com/content/www/us/en/ark/products/191792/intel-core-i79700-processor-12m-cache-up-to-4-70-ghz.html) | 3 GHz | 0xf4 (2022-07-31) | 26 |

| Coffee Lake R | [i9-9900K](https://ark.intel.com/products/186605) | 3.6 GHz | ? | 21 |

| Coffee Lake HR | [i7-9750H](https://ark.intel.com/content/www/us/en/ark/products/191045/intel-core-i7-9750h-processor-12m-cache-up-to-4-50-ghz.html) | 2.6 GHz | 0xf4 (2023-02-23) | 37 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0x32 (2019-07-05) | 135 |

| Ice Lake | [i5-1035G1](https://ark.intel.com/content/www/us/en/ark/products/196603/intel-core-i5-1035g1-processor-6m-cache-up-to-3-60-ghz.html) | 1.00 GHz | 0xb0 (2022-03-09) | 255 |

| Comet Lake | [i9-10900K](https://www.intel.com/content/www/us/en/products/sku/199332/intel-core-i910900k-processor-20m-cache-up-to-5-30-ghz.html) | 3.70 GHz | 0xfc (2024-02-01) | 24 |

| Emerald Rapids | [Xeon Gold 5515+](https://ark.intel.com/content/www/us/en/ark/products/237562/intel-xeon-gold-5515-processor-22-5m-cache-3-20-ghz.html) | 3.2 GHz | 0x21000230 (2024-02-05) | 32 |

**注意(校准)。**

目前,配置可靠定时器间隔的最简单方法是使用 `app/bench` 基准测试工具和长 NOP 滑动,并逐渐增加/减少 `SGX_STEP_TIMER_INTERVAL`。您可以从大约 20 开始,然后执行 `NUM=100 make parse` 来获取 100 条指令 NOP 滑动的单步、零步和多步摘要(一旦您有了更稳定的间隔,您可以切换到更长的滑动)。零步太多表明您需要增加定时器间隔,而多步则需要降低定时器间隔。

**注意(过滤零步)。**

重要提示:当剩下一些零步时不要担心,只要您取得进展,您可以通过查看飞地的代码 PTE 访问位(该位仅在指令实际退休并发生单步时设置)来确定性地过滤掉零步。因此,在配置了保守的定时器间隔以始终避免多步之后,SGX-Step 可以实现_完美的_指令级粒度的无噪声单步执行。

**注意(扩展中断"着陆窗口")。**

如下面的根本原因分析所阐明的,解析 `ERESUME` 后第一个飞地指令(代码)地址的页表遍历越慢,中断"着陆窗口"就越长,因此 SGX-Step 的单步执行可靠性就越高。例如,我们发现,除了清除飞地的 PMD 访问位之外,通过在 `ERESUME` 之前从 CPU 缓存刷新一个或多个不受保护的页表条目,可以进一步扩展着陆窗口,迫使 CPU 在页表遍历期间等待慢速内存。因此,当您找不到可靠的定时器间隔配置时,请确保 (i) 清除飞地的代码 PTE/PMD "访问"位,(ii) 在 AEP 处理程序中刷新(`CLFLUSH`)一个或多个飞地页表条目。

**注意(微码)。**

另一个警告涉及最近的 Foreshadow/ZombieLoad/RIDL/etc 微码缓解措施,这些措施在飞地进入/退出时刷新易受攻击的 uarch 缓冲区。请注意,当启用这些缓解措施时,定时器间隔将需要增加,因为飞地进入需要更长时间(例如,在我 的 i7-8650U CPU 上,我发现单步定时器间隔上升到 54,而使用 Foreshadow 之前的微码仅为 34)。

额外的刷新操作可能还会增加飞地进入时间的方差,这意味着您可能需要更保守地配置定时器,并允许更多零步(可以如上所述确定性地过滤掉)。

### SGX-Step 根本原因分析

关于 SGX-Step 如何可靠地中断臭名昭著复杂的 `ERESUME` 指令之后的第一个(可能非常短的!)飞地指令的详细根本原因分析在 [AEX-Notify](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) 论文中有描述。

我们发现 SGX-Step 成功的关键在于使用"访问"(A) 位。具体来说,SGX-Step 在配置 APIC 触发单次中断之前,始终清除受害飞地页中间目录(PMD)中的 A 位。A 位仅在飞地至少执行一条指令时才会被处理器设置,因此可用于确定性地区分零步和单步。

关键的是,由于处理器的页未命中处理程序针对常见的快速路径进行了优化,并使用慢得多的"微码辅助"来处理不太频繁且更复杂的需要修改 PMD 或 PTE 的情况,这种辅助的效果是将 `ERSUME` 后的第一个飞地指令的执行延长数百个周期。因此,这个"辅助窗口"为粗粒度的、通常分布式的 APIC 定时器中断提供了宽敞的着陆空间,使其能够高精度到达。

## 在您自己的项目中使用 SGX-Step

在您自己的项目中开始使用 SGX-Step 框架的最简单方法是通过 [git 子模块](https://git-scm.com/book/en/v2/Git-Tools-Submodules):

```

$ cd my/git/project

$ git submodule add https://github.com/jovanbulck/sgx-step.git

$ cd sgx-step # Now build `/dev/sgx-step` and `libsgxstep` as described above

```

请查看 `app` 目录中的 Makefile,了解客户端应用程序如何链接到 `libsgxstep` 以及任何本地 SGX SDK/PSW 包。

以下是使用 SGX-Step 的已知项目列表。如果您的项目使用了 SGX-Step 但未包含在下面,请随时提交拉取请求。

| 标题 | 出版物详情 | 源代码 | 使用的 SGX-Step 功能 |

| ---------------------------------------------------------------------------------------------- | -------------------------------------------------------------------------------------------- | ------------------------------------------------------------------------- | ------------------------------------------------------- |

| AEX-NStep: Probabilistic Interrupt Counting Attacks on Intel SGX | [S&P'26](https://arxiv.org/pdf/2510.14675) | [Zenodo](https://zenodo.org/records/17338383) | Page faults, IPIs, WRMSR Interrupt Gate |

| MDPeek: Breaking Balanced Branches in SGX with Memory Disambiguation Unit Side Channels | [ASPLOS'25](https://www.comp.nus.edu.sg/~tcarlson/pdfs/liu2025mbbbiswmdusc.pdf) | [GitHub (Artifact Evaluated & Functional)](https://github.com/CPU-THU/MDPeek) | Page faults |

| Activation Functions Considered Harmful: Recovering Neural Network Weights through Controlled Channels | [ArXiv'25](https://arxiv.org/pdf/2503.19142) | - | Single-stepping, PTE A/D |

| TLBlur: Compiler-Assisted Automated Hardening against Controlled Channels on Off-the-Shelf Intel SGX Platforms | [USEC'25](https://vanbulck.net/files/usenix25-tlblur.pdf) | [GitHub (full)](https://github.com/TLBlur-SGX) | Single-stepping, PTE A/D, page faults |

| POSTER: On the Feasibility of Inferring SGX Execution through PMU | [AsiaCCS'24](https://dl.acm.org/doi/pdf/10.1145/3634737.3659434) | - | Single-stepping, zero-stepping|

| SIGY: Breaking Intel SGX Enclaves with Malicious Exceptions & Signals | [ArXiv'24](https://arxiv.org/abs/2404.13998) | - | Timer interrupts, page faults |

| On (the Lackin) Code Confidentiality in Trusted Execution Environments | [S&P24](https://ivanpuddu.com/files/papers/TEE_WASM_code_Leakage.pdf) | [GitHub (empty)](https://github.com/dn0sar/TEE-WASM-Code-Extraction) | Single-stepping |

| TeeJam: Sub-Cache-Line Leakages Strike Back | [CHES24](https://doi.org/10.46586/tches.v2024.i1.457-500) | [Github (full)](https://github.com/UzL-ITS/teejam) | Single-stepping interrupt latency, PTE A/D |

| AEX-Notify: Thwarting Precise Single-Stepping Attacks through Interrupt Awareness for Intel SGX Enclaves | [USEC23](https://jovanbulck.github.io/files/usenix23-aexnotify.pdf) | [GitHub (SGX SDK mitigation)](https://github.com/intel/linux-sgx/blob/master/sdk/trts/linux/trts_mitigation.S) | Single-Stepping, PTE A/D

| Controlled Data Races in Enclaves: Attacks and Detection | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-chen-sanchuan.pdf) | [GitHub (non-attack)](https://github.com/OSUSecLab/SGXRacer) | Single-stepping, APIC |

| BunnyHop: Exploiting the Instruction Prefetcher | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-zhang-zhiyuan-bunnyhop.pdf) | [GitHub (non-SGX PoC)](https://github.com/0xADE1A1DE/BunnyHop) | Single-stepping, PTE A/D |

| Downfall: Exploiting Speculative Data Gathering | [USEC23](https://www.usenix.org/system/files/usenixsecurity23-moghimi.pdf) | [GitHub (non-SGX PoC)](https://github.com/flowyroll/downfall/tree/main/POC) | Single-stepping, zero-stepping |

| All Your PC Are Belong to Us: Exploiting Non-control-Transfer Instruction BTB Updates for Dynamic PC Extraction | [ISCA23](https://dl.acm.org/doi/pdf/10.1145/3579371.3589100?casa_token=Q5jf5nOgiLIAAAAA:cT0ltJh7vk943buODuR4oMFKmuhg2Tp-djFm2kUu6DzlxtBhNhEw2WteRggn0k99D7ft-P6pluVrFA) | - | Single-stepping |

| Cache-timing attack against HQC | [CHES23](https://eprint.iacr.org/2023/102.pdf) | - | Single-stepping, PTE A/D |

| FaultMorse: An automated controlled-channel attack via longest recurring sequence | [ComSec23](https://www.sciencedirect.com/science/article/pii/S0167404822003959) | [GitHub (post processing)](https://github.com/Ezekiel-1998/FaultMorse) | Page fault |

| AEPIC Leak: Architecturally Leaking Uninitialized Data from the Microarchitecture | [USEC22](https://www.usenix.org/system/files/sec22-borrello.pdf) | [GitHub (full)](https://github.com/IAIK/AEPIC) | Single-Stepping, PTE A/D |

| MoLE: Mitigation of Side-channel Attacks against SGX via Dynamic Data Location Escape | [ACSAC22](https://dl.acm.org/doi/fullHtml/10.1145/3564625.3568002) | - | Single-Stepping, page fault, transient execution |

| WIP: Interrupt Attack on TEE-Protected Robotic Vehicles | [AutoSec22](https://www.ndss-symposium.org/wp-content/uploads/autosec2022_23001_paper.pdf) | - | Single-stepping, multi-stepping |

| Towards Self-monitoring Enclaves: Side-Channel Detection Using Performance Counters | [NordSec22](https://link.springer.com/chapter/10.1007/978-3-031-22295-5_7) | - | Page fault, LVI. |

| ENCLYZER: Automated Analysis of Transient Data Leaks on Intel SGX | [SEED22](https://ieeexplore.ieee.org/document/9935016) | [GitHub (full)](https://github.com/bloaryth/enclyser) | Page-table manipulation |

| Side-Channeling the Kalyna Key Expansion | [CT-RSA22](https://cs.adelaide.edu.au/~yval/pdfs/ChuengsatiansupGYZ22.pdf) | - | Single-Stepping, PTE A/D |

| Rapid Prototyping for Microarchitectural Attacks | [USENIX22](https://www.usenix.org/system/files/sec22summer_easdon.pdf) | [GitHub (full)](https://github.com/libtea/frameworks) | Single-stepping, page fault, PTE A/D, etc. |

| Util::Lookup: Exploiting Key Decoding in Cryptographic Libraries | [CCS21](https://dl.acm.org/doi/abs/10.1145/3460120.3484783) | [GitHub (full)](https://github.com/UzL-ITS/util-lookup) | Single-Stepping, PTE A/D |

| SmashEx: Smashing SGX Enclaves Using Exceptions | [CCS21](https://dl.acm.org/doi/pdf/10.1145/3460120.3484821) | - | Single-stepping |

| Online Template Attacks: Revisited | [CHES21](https://tches.iacr.org/index.php/TCHES/article/view/8967/8545) | [Zenodo (simulation)](https://zenodo.org/record/4680071) | Single-stepping, page fault, PTE A/D |

| Aion Attacks: Manipulating Software Timers in Trusted Execution | [DIMVA21](http://individual.utoronto.ca/shengjiexu/publication/whuang-dimva2021-aion_v2.pdf) | - | Single-stepping, interrupts(?) |

| Platypus: Software-based Power Side-Channel Attacks on x86 | [S&P21](https://platypusattack.com/platypus.pdf) | [GitHub (simulated PoC)](https://github.com/0xhilbert/Platypus) | Single-stepping, zero-stepping |

| CrossTalk: Speculative Data Leaks Across Cores Are Real | [S&P21](https://download.vusec.net/papers/crosstalk_sp21.pdf) | - | Single-stepping, page fault |

| Frontal Attack: Leaking Control-Flow in SGX via the CPU Frontend | [USEC21](https://www.usenix.org/system/files/sec21-puddu.pdf) | [GitHub (full, artifact evaluated)](https://github.com/dn0sar/frontal_poc) | Single-stepping interrupt latency, PTE A/D |

| PThammer: Cross-User-Kernel-Boundary Rowhammer through Implicit Accesses | - | [MICRO20](https://arxiv.org/pdf/2007.08707v2.pdf) | Page table walk |

| SpeechMiner: A Framework for Investigating andMeasuring Speculative Execution Vulnerabilities | [NDSS20](https://www.ndss-symposium.org/wp-content/uploads/2020/02/23105-paper.pdf) | [GitHub (full)](https://github.com/teecert/SpeechMiner) | Page-table manipulation |

| Déjà Vu: Side-Channel Analysis of Mozilla's NSS | [CCS20](https://dl.acm.org/doi/pdf/10.1145/3372297.3421761) | - | Page fault |

| From A to Z: Projective coordinates leakage in the wild | [CHES20](https://eprint.iacr.org/2020/432.pdf) | - | Page fault |

| LVI: Hijacking Transient Execution through Microarchitectural Load Value Injection | [S&P20](https://lviattack.eu/lvi.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step-lvi/tree/master/app/lvi) | Single-stepping, page-table manipulation |

| CopyCat: Controlled Instruction-Level Attacks on Enclaves | [USEC20](https://arxiv.org/pdf/2002.08437.pdf) | - | Single-stepping, page fault, PTE A/D |

| When one vulnerable primitive turns viral: Novel single-trace attacks on ECDSA and RSA | [CHES20](https://eprint.iacr.org/2020/055.pdf) | - | Single-stepping, page fault, PTE A/D |

| Big numbers - Big Troubles: Systematically Analyzing Nonce Leakage in (EC)DSA Implementations | [USEC20](https://www.usenix.org/system/files/sec20summer_weiser_prepub_0.pdf) | - | Page fault |

| Plundervolt: Software-based Fault Injection Attacks against Intel SGX | [S&P20](https://plundervolt.com/doc/plundervolt.pdf) | [GitHub (full)](https://github.com/KitMurdock/plundervolt) | Privileged interrupt/call gates, MSR |

| Bluethunder: A 2-level Directional Predictor Based Side-Channel Attack against SGX | [CHES20](https://heartever.github.io/files/bluethunder_sgx_ches.pdf) | - | Single-stepping |

| Fallout: Leaking Data on Meltdown-resistant CPUs | [CCS19](https://mdsattacks.com/files/fallout.pdf) | - | PTE A/D |

| A Tale of Two Worlds: Assessing the Vulnerability of Enclave Shielding Runtimes | [CCS19](https://people.cs.kuleuven.be/~jo.vanbulck/ccs19-tale.pdf) | [GitHub (full)](https://github.com/jovanbulck/0xbadc0de) | Single-stepping, page fault, PTE A/D |

| ZombieLoad: Cross-Privilege-Boundary Data Sampling | [CCS19](https://zombieloadattack.com/zombieload.pdf) | [GitHub (PoC)](https://github.com/IAIK/ZombieLoad/) | Single-stepping, zero-stepping, page-table manipulation |

| SPOILER: Speculative Load Hazards Boost Rowhammer and Cache Attacks | [USEC19](https://arxiv.org/pdf/1903.00446.pdf) | - | Single-stepping interrupt latency |

| Nemesis: Studying Microarchitectural Timing Leaks in Rudimentary CPU Interrupt Logic | [CCS18](https://people.cs.kuleuven.be/~jo.vanbulck/ccs18.pdf) | [GitHub (full)](https://github.com/jovanbulck/nemesis) | Single-stepping interrupt latency, page fault, PTE A/D |

| Foreshadow: Extracting the Keys to the Intel SGX Kingdom with Transient Out-of-Order Execution | [USEC18](https://foreshadowattack.eu/foreshadow.pdf) | [GitHub (PoC)](https://github.com/jovanbulck/sgx-step/tree/master/app/foreshadow) | Single-stepping, zero-stepping, page-table manipulation |

| Single Trace Attack Against RSA Key Generation in Intel SGX SSL | [AsiaCCS18](https://rspreitzer.github.io/publications/proc/asiaccs-2018-paper-1.pdf) | - | Page fault |

| Off-Limits: Abusing Legacy x86 Memory Segmentation to Spy on Enclaved Execution | [ESSoS18](https://people.cs.kuleuven.be/~jo.vanbulck/essos18.pdf) | [link (full, artifact evaluated)](https://distrinet.cs.kuleuven.be/software/off-limits/) | Single-stepping, IA32 segmentation, page fault |

| SGX-Step: A Practical Attack Framework for Precise Enclave Execution Control | [SysTEX17](https://people.cs.kuleuven.be/~jo.vanbulck/systex17.pdf) | [GitHub (full)](https://github.com/jovanbulck/sgx-step/tree/master/app/bench) | Single-stepping, page fault, PTE A/D |

SGX-Step 是一个开源框架,用于促进 Intel x86 处理器(尤其是 Intel SGX 平台)的侧信道攻击研究。

SGX-Step 由一个对抗性 Linux 内核驱动程序和一个小型用户空间操作系统库组成,允许完全从用户空间配置不受信任的页表条目和/或 x86 APIC 定时器中断。SGX-Step 已被我们的研究以及独立研究人员所利用,实现了多个新的和改进的飞地执行攻击,能够以最高的时间分辨率收集侧信道观察结果(即,在受害飞地执行_每一条_指令后进行中断)。

**许可证。** SGX-Step 是免费软件,采用 [GPLv3](https://www.gnu.org/licenses/gpl-3.0) 许可证。SGX-Step 的标志来源于 Eadweard Muybridge 著名的[公有领域](https://en.wikipedia.org/wiki/Sallie_Gardner_at_a_Gallop)"Sallie Gardner at a Gallop"照片系列,与我们的飞地单步执行目标相似,将奔跑的马动态分解为一系列单独的照片帧,以揭示整体的马步态特性。

| SGX-Step 版本 | 变更日志功能 |

| -------------- | ------------------------------------------------------------------------------ |

| v1.5.0 | 稳定化修复(KPTI,内核 ISR 映射);(实验性)Gramine 移植;IPI 支持。 |

| v1.4.0 | 特权中断/调用门(Plundervolt)。 |

| v1.3.0 | 瞬态执行支持(Foreshadow)。 |

| v1.2.0 | 用户空间中断处理和确定性零步过滤(Nemesis)。 |

| v1.1.0 | IA32 支持。 |

| v1.0.0 | 用户空间页表操作和 APIC 定时器单步执行。 |

**出版物。** SGX-Step 已被多个独立研究小组采用,并开创了一系列高分辨率 SGX 攻击。使用 SGX-Step 的已知项目完整最新列表包含在本文档[底部](#bottom)。原始论文的副本可在[此处](https://jovanbulck.github.io/files/systex17-sgxstep.pdf)获取。

```

@inproceedings{vanbulck2017sgxstep,

title = {{SGX-Step}: A Practical Attack Framework for Precise Enclave Execution Control},

author = {Van Bulck, Jo and Piessens, Frank and Strackx, Raoul},

booktitle = {2nd Workshop on System Software for Trusted Execution {(SysTEX)}},

publisher = {{ACM}},

pages = {4:1--4:6},

month = Oct,

year = 2017,

}

```

**演示。** [app/memcmp](app/memcmp) 目录包含一个演示应用程序,通过单步执行一个包含微妙、非恒定时间 `memcmp` 密码比较逻辑的示例飞地来说明 SGX-Step 攻击的威力。与传统的、臭名昭著的噪声时序攻击不同,SGX-Step 可以_线性_时间确定性逐字符暴力破解密码:

## 概述

与之前的飞地抢占提案相比,SGX-Step 设计的关键在于为保存页表条目的物理内存位置、本地 APIC 内存映射 I/O 配置寄存器以及 x86 中断描述符表(IDT)创建用户空间虚拟内存映射。这允许一个不受信任的、攻击者控制的主机进程轻松地 (i) 跟踪或修改飞地页表条目,(ii) 配置 APIC 定时器单次/周期性中断源,(iii) 触发处理器间中断,以及 (iv) 完全在_用户空间_注册自定义中断处理程序。

上图总结了我们通过框架中断和恢复 SGX 飞地的硬件和软件步骤序列。

1. 本地 APIC 定时器中断在飞地指令内到达。

2. 处理器执行 AEX procedure,将执行上下文安全存储在飞地的 SSA 帧中,初始化 CPU 寄存器,并跳转到 IDT 中注册的用户空间中断处理程序。

3. 此时,任何特定于攻击的间谍代码都可以轻松插入。

4. 库返回到用户空间 AEP 蹦床。我们修改了官方 SGX SDK 的不受信任运行时,以允许轻松注册自定义 AEP 存根。此外,为了在攻击者控制的基准调试飞地上精确评估我们的方法,SGX-Step 可以_可选地_被检测以从被中断飞地的 SSA 帧中检索存储的指令指针(使用 Linux 的 `/proc/self/mem` 接口和 `EDBGRD` 指令)。

5. 之后,我们在执行 (6) `ERESUME` 之前,通过写入初始计数内存映射 I/O 寄存器来为下一次中断配置本地 APIC 定时器。

## 源代码概述

本仓库组织如下:

```

.

├── app -- Collection of sample client applications using SGX-Step to

│ attack different victim enclave scenarios.

├── doc -- Papers and reference material.

├── kernel -- Minimal dynamically loadable Linux kernel driver to export

│ physical memory to user space and bootstrap `libsgxstep`.

├── libsgxstep -- Small user-space operating system library that implements the

│ actual SGX-Step functionality, including x86 page-table and

│ APIC timer manipulations.

└── sdk -- Bindings to use SGX-Step with different SGX SDKs and libOSs.

```

## 框架功能和应用

SGX-Step 是一个通用执行控制框架,能够以_任意_攻击者代码精确地交错受害飞地指令。SGX-Step 框架的一些主要用例总结在下图中(另请参阅本文档[底部](#bottom)的使用 SGX-Step 的出版物最新列表)。

## 构建和运行

### 0. 系统要求

SGX-Step 需要支持 [SGX](https://github.com/ayeks/SGX-hardware) 的 Intel 处理器和现成的 Linux 内核。我们的原始评估是在 i7-6500U/6700 CPU 上进行的,运行 Ubuntu 18.04 和标准 Linux 4.15.0 内核。也支持更新的 Linux 内核和发行版。

我们在下面总结了 Linux [内核参数](https://www.kernel.org/doc/html/latest/admin-guide/kernel-parameters.html)。

| Linux 内核参数 | 动机 |

| ------------------------------------ | ------------------------------------------------------------------------------------------------------------------------------------------------------------------------------ |

| `nox2apic` | 可选配置本地 APIC 设备为内存映射 I/O 模式(以使用 SGX-Step 的精确单步执行功能)。如果设置此参数,请确保在 libsgxstep/config.h 中将 X2APIC 设置为 0。或者,您可以让 CPU 保持在 x2APIC 模式,最近的 SGX-Step 发行版也应该兼容。 |

| `iomem=relaxed no_timer_check` | 抑制内核日志中不需要的警告消息。 |

| `nmi_watchdog=0` | 抑制内核 NMI 看门狗。 |

| `isolcpus=1` | 将受害进程绑定到隔离的 CPU 核心。 |

| `clearcpuid=308,295,514` | 禁用监督模式访问预防(SMAP,位 295)、监督模式执行预防(SMEP,位 308)和用户模式指令预防(UMIP,位 514)功能。 |

| `pti=off` | 禁用内核页表隔离(以避免用户 IRQ 处理程序导致内核崩溃)。 |

| `rcupdate.rcu_cpu_stall_suppress=1` | 禁用内核的读-复制更新(RCU)CPU 停滞检测器(以避免长时间单步执行而不调用内核定时器中断处理程序时产生警告。) |

| `msr.allow_writes=on` | 抑制 SGX-Step 对模型特定寄存器(MSR)写入的内核警告消息。 |

| `vdso=0` | 仅在最近的 Linux 内核上:禁用 vdso_sgx_enter_enclave 库(与 AEP 拦截补丁不兼容)。 |

| `dis_ucode_ldr` | 可选禁用 CPU 微码更新(最近的瞬态执行攻击缓解可能需要重新校准单步执行间隔)。 |

按如下方式将所需的启动参数传递给内核:

```

# if you don't have vim, use nano instead

$ sudo vim /etc/default/grub

# Add the following line: GRUB_CMDLINE_LINUX_DEFAULT="quiet splash iomem=relaxed no_timer_check clearcpuid=308,295,514 pti=off isolcpus=1 nmi_watchdog=0 rcupdate.rcu_cpu_stall_suppress=1 msr.allow_writes=on vdso=0"

$ sudo update-grub && reboot

```

要检查当前运行的内核配置是否正确,请执行:

```

$ sudo ./check_sys.sh

.. Checking recommended SGX-Step parameters [OK]

.. Checking unknown kernel parameters [OK]

.. Checking CPU features [OK]

.. Checking kernel page-table isolation [OK]

```

最后,为了提高整体执行时间稳定性,您可以选择在 BIOS 配置中禁用 C-States 和 SpeedStep 技术。

### 1. 构建和加载 `/dev/sgx-step`

SGX-Step 带有一个可加载内核模块,向 `libsgxstep` 用户空间库导出 IOCTL 接口。驱动程序主要负责 (i) 挂钩 APIC 定时器中断处理程序,(ii) 收集不受信任的页表映射,以及 (iii) 可选地获取被中断的基准飞地的指令指针。

要构建和加载 `/dev/sgx-step` 驱动程序,请执行:

```

$ cd kernel/

$ ./install_SGX_driver.sh # tested on Ubuntu 20.04/22.04

$ make clean load

```

**注意(/dev/sgx_enclave)。** SGX-Step 支持传统 Intel `/dev/isgx` 树外驱动程序(应该适用于所有平台),以及适用于具有最新 Linux 内核 >5.11 且支持灵活启动控制的平台的树内 `/dev/sgx_enclave` 驱动程序。`install_SGX_driver.sh` 脚本应自动检测树内 `/dev/sgx-enclave` 驱动程序是否可用,如果不可用,则通过指向未修改的 v2.14 [linux-sgx-driver](_URL_9/>) 的 git 子模块构建和加载树外 `/dev/isgx` 驱动程序。

**注意(/dev/mem)。** 我们依赖 Linux 的虚拟 `/dev/mem` 设备来构建 APIC 物理内存映射 I/O 寄存器和感兴趣页表条目的用户级虚拟内存映射。然而,最近的 Linux 发行版通常启用 `CONFIG_STRICT_DEVMEM` 选项来阻止这种使用。因此,我们的 `/dev/sgx-step` 驱动程序包含一种[方法](https://www.libcrack.so/index.php/2012/09/02/bypassing-devmem_is_allowed-with-kprobes/)来绕过 `devmem_is_allowed` 检查,而无需重新编译内核。

### 2. 补丁和安装 SGX SDK

为了轻松注册自定义异步退出指针(AEP)存根,我们修改了官方 Intel SGX SDK 的不受信任运行时。按以下步骤检出 [linux-sgx](https://github.com/01org/linux-sgx) v2.23 并应用我们的补丁。

```

$ cd sdk/intel-sdk/

$ ./install_SGX_SDK.sh # tested on Ubuntu 20.04/22.04

$ source /opt/intel/sgxsdk/environment # add to ~/.bashrc to preserve across terminal sessions

$ sudo service aesmd status # stop/start aesmd service if needed

```

上述安装脚本已在 Ubuntu 22.04 LTS 上测试。

对于其他 GNU/Linux 发行版,请按照 [linux-sgx](https://github.com/01org/linux-sgx) 项目中的说明构建和安装 Intel SGX SDK 和 PSW 包。您还需要构建和加载一个(未修改的)[linux-sgx-driver](https://github.com/01org/linux-sgx-driver) SGX 内核模块才能使用 SGX-Step。

**注意(本地安装)。** 补丁 SGX SDK 和 PSW 包可以本地安装,而不会影响兼容的系统级 'linux-sgx' 安装。为此,示例 Makefile 支持指向本地 SDK 安装目录的 `SGX_SDK` 环境变量。当检测到非默认 SDK 路径(即不是 `/opt/intel/sgxsdk`)时,"run" Makefile 目标还会动态链接到本地 `linux-sgx` 目录中构建的补丁 `libsgx_urts.so` 不受信任运行时(使用 `LD_LIBRARY_PATH` 环境变量)。

**注意(32 位支持)。** 构建 32 位版本 SGX SDK 和 SGX-Step 的说明(已过时且未维护!)可在 [README-m32.md](README-m32.md) 中找到。

### 3. 构建和运行测试应用程序

用户空间应用程序可以链接到 `libsgxstep` 库以使用 SGX-Step 的单步执行和页表操作功能。请查看 "app" 目录中的示例应用程序。

首先,检查 APIC 和中断描述符表设置:

```

$ cd app/selftest/idt

$ make run # fires interrupts in an infinite loop to stress-test stability; exit with CTRL-C

```

例如,要构建和运行一个测试页表操作功能和 SDK 补丁的基本示例应用程序:

```

$ cd app/aep-redirect

$ make run

```

要测试定时器单步执行功能,可以尝试构建和运行一个基准飞地来单步执行 100 个连续的 `nop` 指令:

```

$ cd app/bench

$ NUM=100 make parse # alternatively vary NUM and use STRLEN=1 or ZIGZAG=1

```

上述命令构建 `libsgxstep`、基准受害飞地和不受信任的攻击者主机进程,其中攻击场景和实例大小通过相应的环境变量配置。该命令还非交互式运行生成的二进制文件(以确保确定性定时器间隔),最后调用特定于攻击的后处理 Python 脚本来解析生成的飞地指令指针基准结果。

**注意(性能)。** 单步执行飞地执行会产生相当大的减速。我们测量到论文中描述的实验执行时间长达 15 分钟。SGX-Step 的页表操作功能允许仅对选定函数启动单步执行,例如通过撤销特定感兴趣代码或数据页的访问权限。

**注意(定时器间隔)。** 确切的定时器间隔值取决于 CPU 频率,因此本质上仍然是平台特定的(另请参阅 [app/selftest/apic](app/selftest/apic) 了解评估各种 APIC 定时器模式准确性的详细微基准测试)。在 `/app/bench/main.c` 中配置合适的值。我们通过调整和观察 NOP 微基准测试飞地指令指针跟踪结果,为我们的评估平台确定了精确的定时器间隔(见下表),如下所述。

**注意(稳定性)。** 为了避免 Linux 内核卡住或崩溃,SGX-Step 应在退出 `libsgxstep` 进程后自动恢复中断描述符表和本地 APIC 定时器。您可以按如下方式检查 APIC 定时器是否仍在所有核心上触发:

```

$ watch -n0.1 "cat /proc/interrupts | grep 'Local timer interrupts'"

```

## 校准单步执行间隔

下表列出了当前支持的 Intel CPU 及其单步执行 APIC 定时器间隔(`libsgxstep/config.h`)。

请注意,确切的单步执行间隔可能取决于处理器的微码版本,当最近的[瞬态执行攻击](https://transient.fail/) 缓解措施在飞地进入/退出时刷新微架构缓冲区时更是如此。下表中提供了一些不同的微码版本作为参考。

| 型号名称 | CPU | 基础频率 | 微码(日期) | APIC 定时器间隔 |

| ------------- | --------------------------------------------------------------------------------------------------------------------------------------- | -------------- | ----------------------- | ------------------- |

| Skylake | [i7-6700](https://ark.intel.com/products/88196) | 3.4 GHz | ? | 19 |

| Skylake | [i7-6500U](https://ark.intel.com/products/88194) | 2.5 GHz | ? | 25 |

| Skylake | [i5-6200U](https://ark.intel.com/products/88193) | 2.3 GHz | ? | 28 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | ? | 34 |

| Kaby Lake R | [i7-8650U](https://ark.intel.com/products/124968) | 1.9 GHz | 0xca (2019-10-03) | 54 |